参数资料

| 型号: | CS4352-CZZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 5/20页 |

| 文件大小: | 0K |

| 描述: | IC DAC STER 102DB 192KHZ 20TSSOP |

| 标准包装: | 74 |

| 位数: | 24 |

| 数据接口: | 串行 |

| 转换器数目: | 2 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 158mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 管件 |

| 输出数目和类型: | 2 电压,单极 |

| 采样率(每秒): | 192k |

| 产品目录页面: | 757 (CN2011-ZH PDF) |

| 配用: | 598-1518-ND - BOARD EVAL FOR CS4352 DAC |

| 其它名称: | 598-1186-5 |

DS684F2

13

CS4352

4.4

De-Emphasis Control

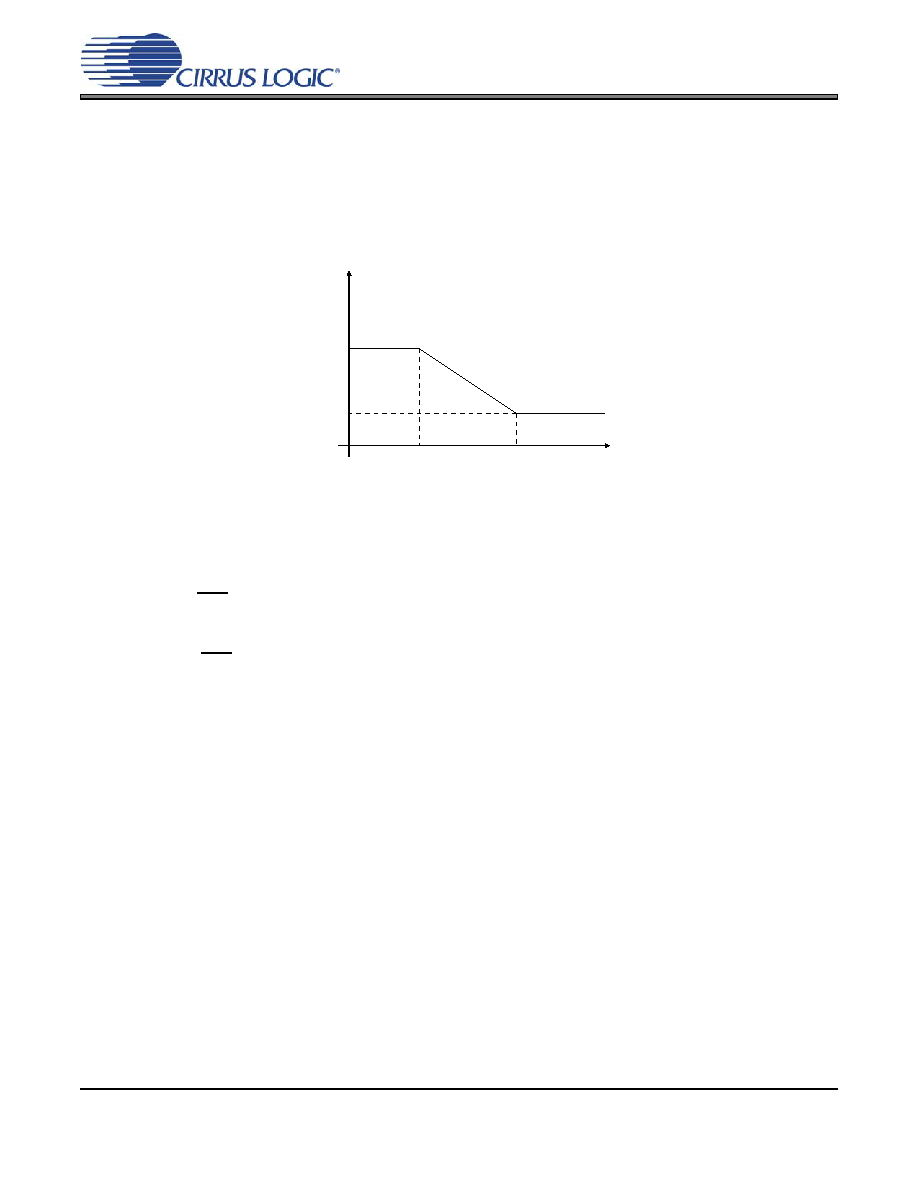

The device includes on-chip digital de-emphasis. Figure 6 shows the de-emphasis curve for Fs equal to

44.1 kHz. The frequency response of the de-emphasis curve scales with changes in sample rate, Fs. The

De-emphasis error will increase for sample rates other than 44.1 kHz

When pulled to VL, the DEM pin activates the 44.1 kHz de-emphasis filter. When pulled to GND, the DEM

pin turns off the de-emphasis filter.

Note:

De-emphasis is only available in Single-Speed Mode.

4.5

Recommended Power-Up Sequence

1.

Hold RST low until the power supplies and configuration pins are stable, and the master and left/right

clocks are locked to the appropriate frequencies, as discussed in Section 4.2. In this state, VQ will re-

main low and VBIAS will be connected to VA.

2.

Bring RST high. The device will remain in a low power state with VQ low and will initiate the power-up

sequence after approximately 512 LRCK cycles in Single-Speed Mode (1024 LRCK cycles in Double-

Speed Mode, and 2048 LRCK cycles in Quad-Speed Mode).

4.6

Grounding and Power Supply Arrangements

As with any high-resolution converter, the CS4352 requires careful attention to power supply and grounding

arrangements if its potential performance is to be realized. Figure 2 shows the recommended power ar-

rangements, with VA_H, VA, VD, and VL connected to clean supplies. If the ground planes are split between

digital ground and analog ground, the GND pins of the CS4352 should be connected to the analog ground

plane.

All signals, especially clocks, should be kept away from the VBIAS and VQ pins in order to avoid unwanted

coupling into the DAC.

4.6.1

Capacitor Placement

Decoupling capacitors should be placed as close to the DAC as possible, with the low-value ceramic ca-

pacitor being the closest. To further minimize impedance, these capacitors should be located on the same

layer as the DAC. If desired, all supply pins may be connected to the same supply, but a decoupling ca-

pacitor should still be placed on each supply pin.

Note:

All decoupling capacitors should be referenced to analog ground.

The CDB4352 evaluation board demonstrates the optimum layout and power supply arrangements.

Gain

dB

-10dB

0dB

Frequency

T2 = 15 s

T1=50 s

F1

F2

3.183 kHz

10.61 kHz

Figure 6. De-Emphasis Curve

相关PDF资料 |

PDF描述 |

|---|---|

| MS27473E24A29S | CONN PLUG 29POS STRAIGHT W/SCKT |

| MS27496E19B32PA | CONN RCPT 32POS BOX MNT W/PINS |

| MS3102R36-1S | CONN RCPT 22POS BOX MNT W/SCKT |

| M83723/96R12126 | CONN PLUG 12POS STRAIGHT W/PINS |

| MS27474E16A6S | CONN RCPT 6POS JAM NUT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4352-CZZR | 功能描述:数模转换器- DAC IC 102dB 192kHz Str DAC w/Line Drivr RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| CS4352-DZZ | 功能描述:数模转换器- DAC Stereo DAC w/Ln Drvr 24-Bit 192kHz 102dB RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| CS4352-DZZR | 功能描述:数模转换器- DAC IC 102dB 192kHz Str DAC w/Line Drivr RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| CS4353 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:3.3 V Stereo Audio DAC with 2 VRMS Line Output |

| CS4353_09 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:3.3 V Stereo Audio DAC with 2 VRMS Line Output |

发布紧急采购,3分钟左右您将得到回复。