参数资料

| 型号: | CS5342-CZZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 9/21页 |

| 文件大小: | 0K |

| 描述: | IC ADC AUD 105DB 200KHZ 16-TSSOP |

| 标准包装: | 96 |

| 位数: | 24 |

| 采样率(每秒): | 200k |

| 数据接口: | 串行 |

| 转换器数目: | 2 |

| 电压电源: | 模拟和数字 |

| 工作温度: | -10°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 16-TSSOP |

| 包装: | 管件 |

| 输入数目和类型: | 2 个单端,单极 |

| 产品目录页面: | 755 (CN2011-ZH PDF) |

| 其它名称: | 598-1688 |

DS608F1

17

CS5342

4.4

Power-Up Sequence

Reliable power-up can be accomplished by keeping the device in reset until the power supplies, clocks and

configuration pins are stable. It is also recommended that reset be enabled if the analog or digital supplies

drop below the minimum specified operating voltages to prevent power-glitch-related issues.

4.5

Analog Connections

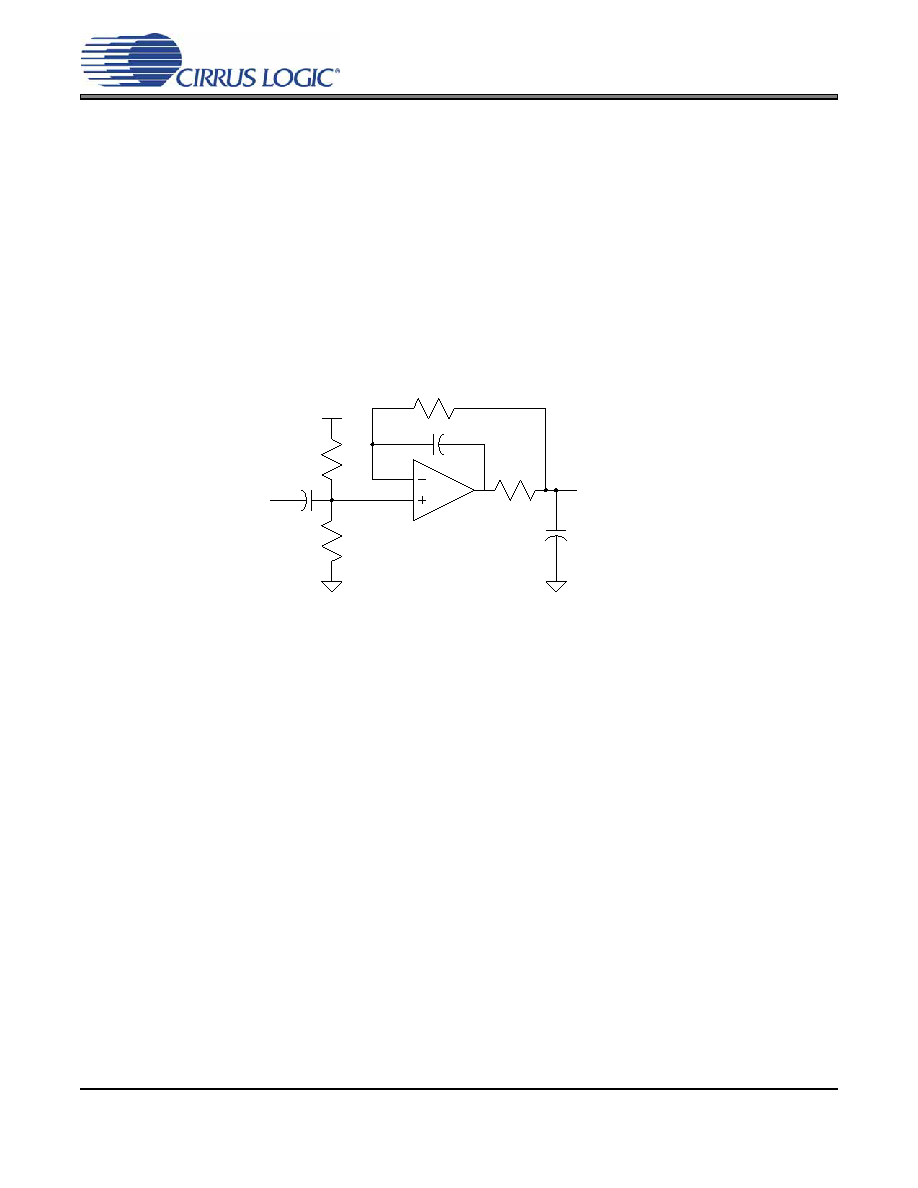

The analog modulator samples the input at 6.144 MHz. The digital filter rejects signals within the stopband

of the filter. However, there is no rejection for input signals that are multiples of the input sampling frequency

(n

× 6.144 MHz), where n=0, 1, 2, .... Figure 21 shows the suggested filter that attenuates any noise energy

at 6.144 MHz and provides the optimum source impedance for the modulators. The use of capacitors that

have a large voltage coefficient (such as general-purpose ceramics) must be avoided because these can

degrade signal linearity.

4.6

Grounding and Power Supply Decoupling

As with any high-resolution converter, the CS5342 requires careful attention to power supply and grounding

arrangements if its potential performance is to be realized. Figure 17 shows the recommended power ar-

rangements, with VA and VL connected to clean supplies. VD, which powers the digital filter, may be run

from the system logic supply or powered from the analog supply via a resistor. In this case, no additional

devices should be powered from VD. Decoupling capacitors should be as near to the ADC as possible, with

the low value ceramic capacitor being the nearest. All signals, especially clocks, should be kept away from

the FILT+ and VQ pins in order to avoid unwanted coupling into the modulators. The FILT+ and VQ decou-

pling capacitors, particularly the 0.1 F, must be positioned to minimize the electrical path from FILT+ and

REF_GND. The CDB5342 evaluation board demonstrates the optimum layout and power supply arrange-

ments. To minimize digital noise, connect the ADC digital outputs only to CMOS inputs.

4.7

Synchronization of Multiple Devices

In systems where multiple ADCs are required, care must be taken to achieve simultaneous sampling. To

ensure synchronous sampling, the MCLK and LRCK must be the same for all of the CS5342’s in the system.

4.8

Capacitor Size on the Reference Pin (FILT+)

The CS5342 requires an external capacitance on the internal reference voltage pin, FILT+. The size of this

decoupling capacitor affects the low frequency distortion performance, as shown in Figure 22, with larger

capacitor values used to optimize low frequency distortion performance. The THD+N curves in Figure 22

Figure 21. CS5342 Recommended Analog Input Buffer

100 k

100 k

VA

4.7

F

470 pF

C0G

634

91

2700 pF

CS5342 AINx

AINx

相关PDF资料 |

PDF描述 |

|---|---|

| CS5345-CQZ | IC ADC AUD 104DB 200KHZ 48-LQFP |

| CS5345-DQZ | IC ADC AUD 104DB 200KHZ 48-LQFP |

| CS5346-CQZR | IC ADC AUD 103DB 200KHZ 48-LQFP |

| CS5351-BZZ | IC ADC AUD 108DB 204KHZ 24-TSSOP |

| CS5361-DZZ | IC ADC AUD 114DB 204KHZ 24-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5342-CZZR | 功能描述:音频模/数转换器 IC IC 105dB 192 kHz Multi-bit Audio ADC RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装: |

| CS5342-DZZ | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:105 dB, 192 kHz, MULTI-BIT AUDIO A/D CONVERTER |

| CS5343 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:98 dB, 96 kHz, Multi-Bit Audio A/D Converter |

| CS5343_07 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:98 dB, 96 kHz, Multi-Bit Audio A/D Converter |

| CS5343_08 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:98 dB, 96 kHz, Multi-Bit Audio A/D Converter |

发布紧急采购,3分钟左右您将得到回复。