- 您现在的位置:买卖IC网 > PDF目录10672 > CS5364-CQZ (Cirrus Logic Inc)IC ADC 4CH 114DB 216KHZ 48-LQFP PDF资料下载

参数资料

| 型号: | CS5364-CQZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 14/42页 |

| 文件大小: | 0K |

| 描述: | IC ADC 4CH 114DB 216KHZ 48-LQFP |

| 标准包装: | 250 |

| 位数: | 24 |

| 采样率(每秒): | 216k |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 580mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 托盘 |

| 输入数目和类型: | 4 个差分,单极 |

| 产品目录页面: | 755 (CN2011-ZH PDF) |

| 配用: | CDB5364-ND - EVALUATION BOARD FOR CS5364 |

| 其它名称: | 598-1088 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页

DS625F4

21

CS5364

4.4

Master and Slave Operation

CS5364 operation depends on two clocks that are synchronously derived from MCLK: SCLK and LRCK/FS.

See Section 4.5 on page 22 for a detailed description of SCLK and LRCK/FS.

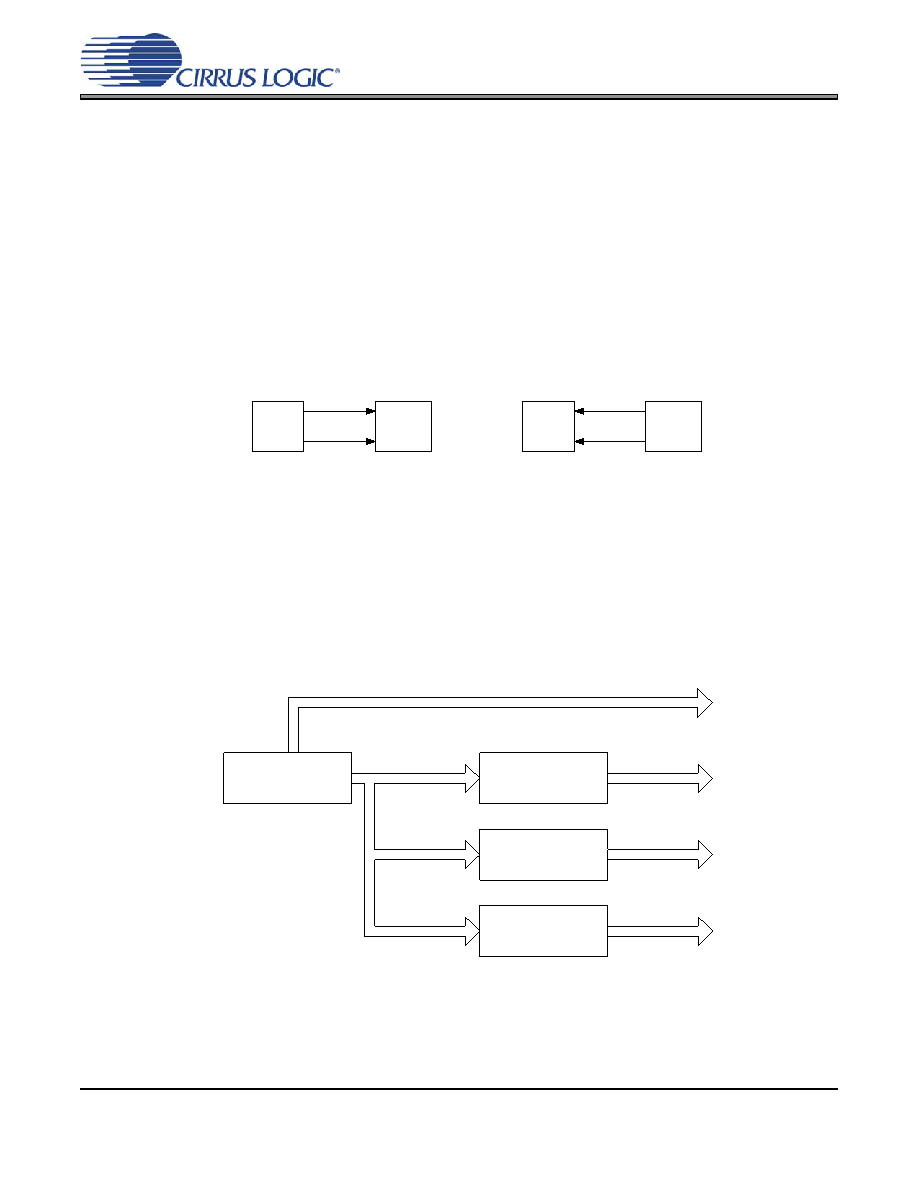

The CS5364 can operate as either clock master or clock slave with respect to SCLK and LRCK/FS. In Mas-

ter Mode, the CS5364 derives SCLK and LRCK/FS synchronously from MCLK and outputs the derived

clocks on the SCLK pin (pin 25) and the LRCK/FS pin (pin 24), respectively. In Slave Mode, the SCLK and

LRCK/FS are inputs, and the input signals must be synchronously derived from MCLK by a separate device

such as another CS5364 or a microcontroller. Figure 8 illustrates the clock flow of SCLK and LRCK/FS in

both Master and Slave Modes.

The Master/Slave operation is controlled through the settings of M1 and M0 pins in Stand-Alone Mode or

by the M[1] and M[0] bits in the Global Mode Control Register in Control Port Mode. See Section 4.6 on page

23 for more information regarding the configuration of M1 and M0 pins or M[1] and M[0] bits.

Figure 8. Master/Slave Clock Flow

4.4.1

Synchronization of Multiple Devices

To ensure synchronous sampling in applications where multiple ADCs are used, the MCLK and LRCK must

be the same for all CS5364 devices in the system. If only one master clock source is needed, one solution

is to place one CS5364 in Master Mode, and slave all of the other devices to the one master, as illustrated

in Figure 9. If multiple master clock sources are needed, one solution is to supply all clocks from the same

external source and time the CS5364 reset de-assertion with the falling edge of MCLK. This will ensure that

all converters begin sampling on the same clock edge.

Figure 9. Master and Slave Clocking for a Multi-Channel Application

ADC as

clock

master

Controller

LRCK/FS

SCLK

ADC as

clock

slave

Controller

LRCK/FS

SCLK

Master

ADC

Slave1

ADC

Slave2

ADC

Slave3

ADC

SCLK & LRCK/FS

相关PDF资料 |

PDF描述 |

|---|---|

| VE-2WR-IX-B1 | CONVERTER MOD DC/DC 7.5V 75W |

| NCS2202SQ2T2G | IC COMPARATOR LV LP OD SC70-5 |

| LTC1420CGN#PBF | IC ADC 12BIT 10MSPS SAMPL 28SSOP |

| VE-2WP-IX-B1 | CONVERTER MOD DC/DC 13.8V 75W |

| VE-2WJ-IX-B1 | CONVERTER MOD DC/DC 36V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5364-CQZR | 功能描述:音频模/数转换器 IC IC 114dB 192kHz 4ch ADC w/TDM Intrfc RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装: |

| CS5364-DQZ | 功能描述:音频模/数转换器 IC 114dB 192kHz 4-Ch ADC w/TDM Interface RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装: |

| CS5364-DQZR | 功能描述:音频模/数转换器 IC IC 114dB 192kHz 4ch ADC w/TDM Intrfc RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装: |

| CS5366 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:114 dB, 192 kHz, 6-Channel A/D Converter |

| CS5366_08 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:114 dB, 192 kHz, 6-Channel A/D Converter |

发布紧急采购,3分钟左右您将得到回复。