参数资料

| 型号: | CS5371-BSZR |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 5/22页 |

| 文件大小: | 0K |

| 描述: | IC MODULATOR LP/HP 1CH 24-SSOP |

| 标准包装: | 1,000 |

| 类型: | 调制器 |

| 分辨率(位): | 24 b |

| 采样率(每秒): | 512k |

| 电压电源: | 模拟和数字 |

| 电源电压: | ±2.5V,3.3 V ~ 5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 24-SSOP |

| 包装: | 带卷 (TR) |

| 配用: | 598-1778-ND - EVALUATION BOARD FOR CS5376 |

CS5371 CS5372

DS255F3

13

bit stream at 512 kbits per second when operated

from a 2.048 MHz modulator clock.

7.1.

Modulator Clock - MCLK

For proper operation, the CS5371/72 modulators

must be provided with a CMOS compatible clock

on the MCLK pin. MCLK is internally divided by

four to generate the modulator sampling clock.

MCLK must have less than 300 ps of in-band jitter

to maintain full performance specifications.

When used with the CS5376A or CS5378 digital fil-

ter, MCLK is automatically generated and is typi-

cally 2.048 MHz or 1.024 MHz.

MCLK can be

generated by other means, using a crystal oscilla-

tor for example, and can run any rate between

100 kHz and 2.2 MHz. If MCLK is disabled, the

modulators are automatically placed into a micro-

power state. They are equipped with loss of clock

detection circuitry to force power down if MCLK is

removed.

The choice of MCLK frequency affects the perfor-

mance of the CS5371/72 modulators. They exhibit

the best dynamic range (SNR) performance with

faster MCLK rates because of increased oversam-

pling of the analog input signal. The modulators

exhibit the best total harmonic distortion (THD)

performance with slower MCLK rates because

slower sampling allows more time to settle the an-

alog input signal.

7.2.

Modulator Data - MDATA

The CS5371/72 modulators output a

Σ serial bit-

stream to the MDATA pin, with a one’s density pro-

portional to the amplitude of the analog input signal

and a bit rate determined by the modulator sam-

pling clock. The modulator sampling clock is a di-

vide by four of MCLK, so for a 2.048 MHz MCLK

the modulator sampling clock and MDATA output

bit rate will be 512 kHz.

The MDATA output has a one’s density defined as

nominal 50% for no signal input, 86% for positive

full scale, and 14% for negative full scale. It has a

maximum positive over-range capability to 93%

and a maximum negative over-range capability to

7%. The one’s density of the MDATA output is de-

fined as the ratio of ‘1’ bits to total bits in the serial

bitstream output, i.e. an 86% one’s density has, on

average, a ‘1’ value in 86 of every 100 output data

bits.

When operated with the CS5376A or CS5378 dig-

ital filter, the full-scale 24-bit output codes range

from 0x5D1C41 to 0xA2EAAE with the internal

OFST disabled.

Note that for a full-scale input signal, 5 Vpp with

VREF=2.5 V, the CS5371/72 and CS5376A/78

chipset does not output a maximum 24-bit 2’s com-

plement digital code of 0x7FFFFF, but instead a

lower scaled value to allow over-range capability.

7.3.

Modulator Sync - MSYNC

To synchronize the analog sampling instant and

timing

of

the

digital

output

bitstream,

the

CS5371/72 modulators use an MSYNC signal.

When using the CS5376A or CS5378 digital filter,

MSYNC is automatically generated from a SYNC

signal input from the external system.

The MSYNC input is rising edge triggered and re-

sets the internal MCLK counter-divider so the ana-

log sampling instant occurs during a consistent

MCLK phase. It also sets the MDATA output tim-

ing so the bitstream can be properly sampled by

the digital filter input.

7.4.

Modulator Flag - MFLAG

The CS5371/72 modulators are 4th order

Σ and

are therefore conditionally stable. The modulators

may go into an oscillatory condition if the analog in-

puts are over-ranged more than 5% past either

positive or negative fullscale.

If an unstable condition is detected, the modulators

collapse to a 1st order system until loop stability is

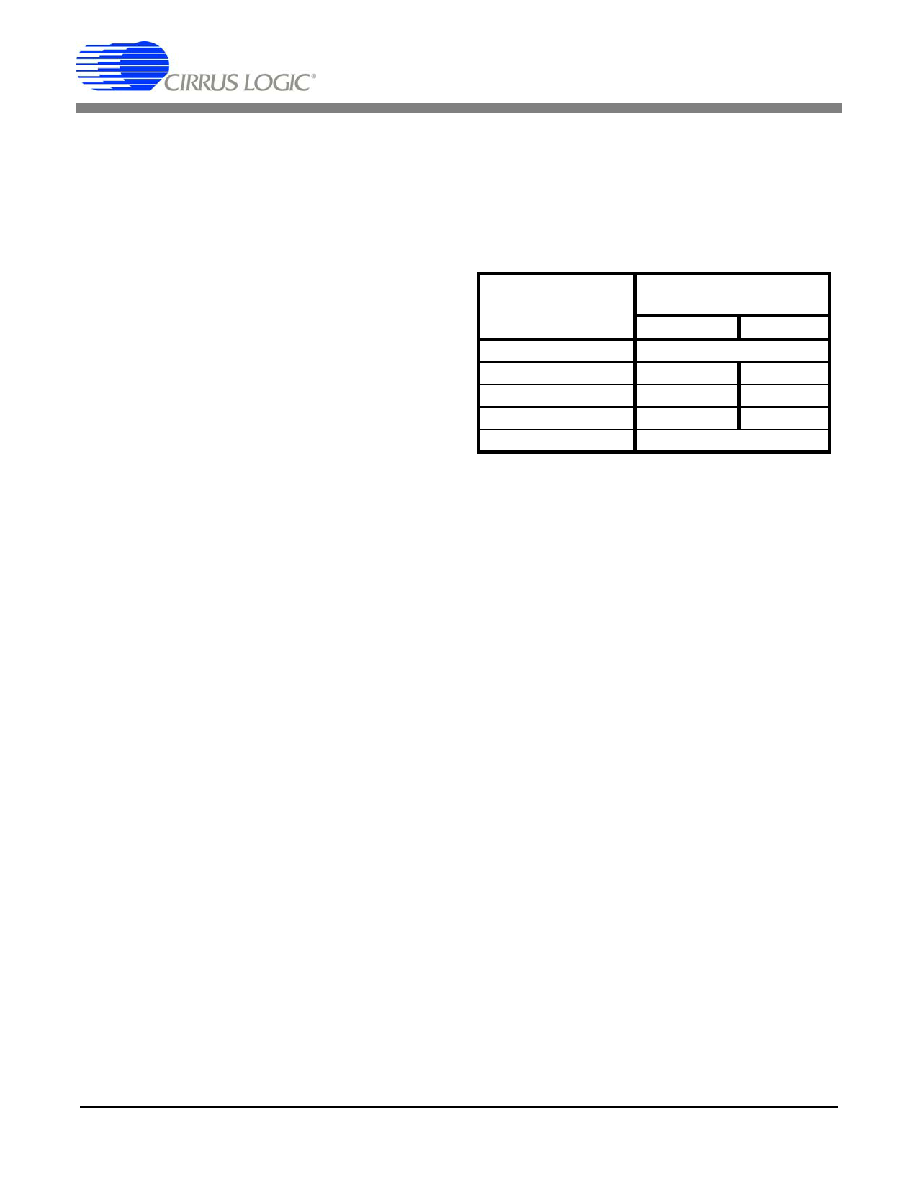

Table 1. Output coding for the CS5371/72 and digital

filter combination

Modulator Input

Signal

Digital Filter

Output Code

OFST=0

OFST=1

> + (VREF + 5%)

Error Flag Possible

+VREF

5D1C41

5B3A71

0V

000000

FE21D8

-VREF

A2EAAE

A108DE

> - (VREF + 5%)

Error Flag Possible

相关PDF资料 |

PDF描述 |

|---|---|

| VI-2WY-MY-S | CONVERTER MOD DC/DC 3.3V 33W |

| VI-2WY-MW-S | CONVERTER MOD DC/DC 3.3V 66W |

| DS1077Z-125+ | IC ECONOSCILLATOR 125MHZ 8SOIC |

| VE-B41-IU-F2 | CONVERTER MOD DC/DC 12V 200W |

| AD7400AYRWZ-RL | IC MODULATOR SIGMA-DELTA 16SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5372 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:LOW POWER HIGH PERFORMANCE MODULATORS |

| CS5372A | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low-power, High-performance Modulators |

| CS5372A-IS | 功能描述:接口 - 专用 LP High Performance Delta Sigma Mod. RoHS:否 制造商:Texas Instruments 产品类型:1080p60 Image Sensor Receiver 工作电源电压:1.8 V 电源电流:89 mA 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:BGA-59 |

| CS5372A-ISR | 功能描述:接口 - 专用 LP High Performance Delta Sigma Mod. RoHS:否 制造商:Texas Instruments 产品类型:1080p60 Image Sensor Receiver 工作电源电压:1.8 V 电源电流:89 mA 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:BGA-59 |

| CS5372A-ISZ | 功能描述:接口 - 专用 IC LP Hgh Prfrmnc Delta Sigma Modultr RoHS:否 制造商:Texas Instruments 产品类型:1080p60 Image Sensor Receiver 工作电源电压:1.8 V 电源电流:89 mA 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:BGA-59 |

发布紧急采购,3分钟左右您将得到回复。