- 您现在的位置:买卖IC网 > PDF目录380127 > CY2DP314OXI (CYPRESS SEMICONDUCTOR CORP) CAT5 AUDIO/VIDEO COMPUTER TRANSMITTER PDF资料下载

参数资料

| 型号: | CY2DP314OXI |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | 时钟及定时 |

| 英文描述: | CAT5 AUDIO/VIDEO COMPUTER TRANSMITTER |

| 中文描述: | 2DP SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 封装: | 5.30 MM, LEAD FREE, SSOP-20 |

| 文件页数: | 4/9页 |

| 文件大小: | 213K |

| 代理商: | CY2DP314OXI |

CY2DP314

Document #: 38-07550 Rev.*E

Page 4 of 9

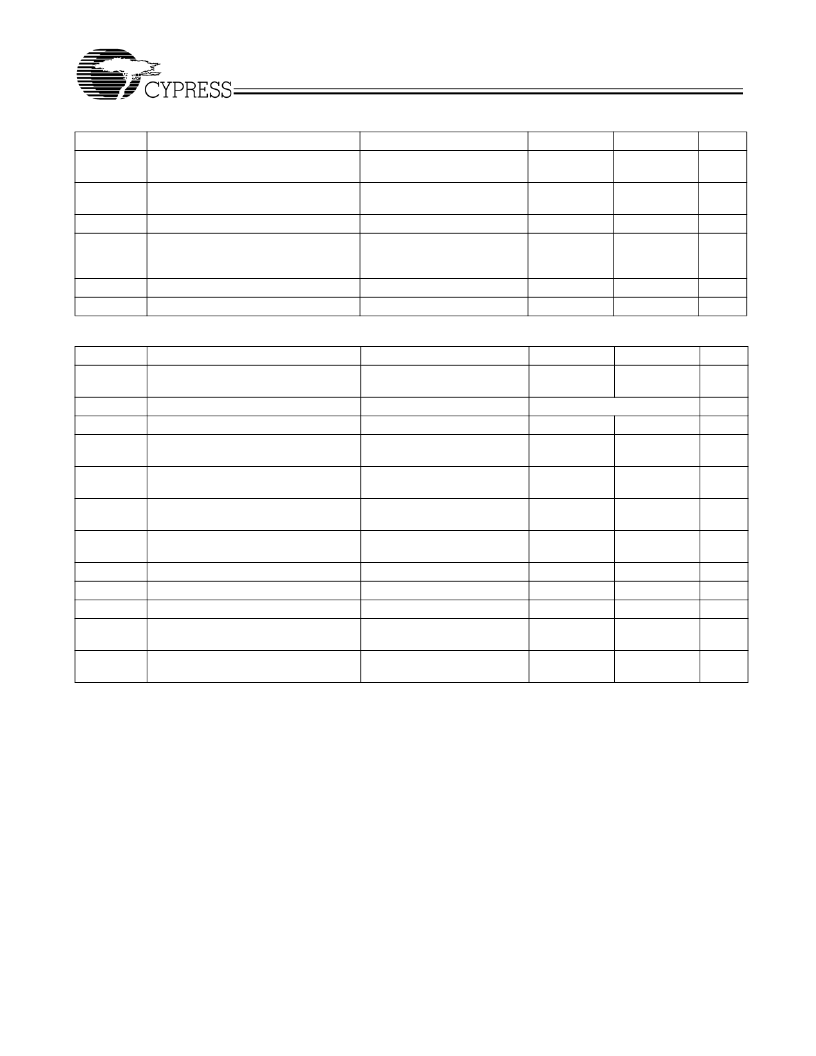

ECL DC Electrical Specifications

.

Parameter

V

EE

Description

Condition

Min.

–2.625

–3.465

V

EE

+ 1.2

Max.

–2.375

–3.135

0V

Unit

V

Negative Power Supply

–2.5V ± 5%, V

CC

= 0.0V

–3.3V ± 5%, V

CC

= 0.0V

Differential operation

V

CMR

ECL Input Differential cross point

voltage

[7]

Output High Voltage

Output Low Voltage

V

EE

= –3.3V ± 5%

V

EE

= –2.5V ± 5%

Input Voltage, High

Input Voltage, Low

V

V

OH

V

OL

I

OH

= –30 mA

[9]

I

OL

= –5 mA

[9]

–1.25

–0.7

V

–1.995

–1.995

–1.165

–1.945

[10]

–1.5

–1.3

V

V

IH

V

IL

Single-ended operation

Single-ended operation

–0.880

[10]

–1.625

V

V

AC Electrical Specifications

Parameter

V

PP

Description

Condition

Min.

0.1

Max.

1.3

Unit

V

ECL/PECL Input Differential Input

Voltage

[7]

Output Common Voltage Range (typ.)

Input Frequency

Propagation Delay CLKA or CLKB to

Output pair

[12]

HSTL Differential Input Voltage

[11]

Differential operation

V

CMRO

F

CLK

T

PD

V

CC

– 1.425

V

50% duty cycle Standard load

PECL, ECL = 660 MHz

HSTL < 1GHz

Duty Cycle Standard Load

Differential Operation

Standard Load Differential

Operation

< 1 GHz

–

1.5

650

750

1.9

GHz

ps

ps

V

280

280

0.4

V

DIF

V

X

HSTL Input Differential Crosspoint Volt-

age

[8]

Output Voltage (peak-to-peak; see

Figure 2)

Output-to-output Skew

Part-to-Part Output Skew

Output Period Jitter (rms)

[13]

Output Pulse Skew

[14]

0.68

0.9

V

Vo

0.375

–

V

tsk

(0)

tsk

(PP)

T

PER

tsk

(P)

660 MHz

[12]

, See Figure 3

660 MHz

[12]

660 MHz

[12]

660 MHz

[12]

, See Figure 3

–

–

–

–

50

150

0.8

50

ps

ps

ps

ps

T

R

,T

F

Output Rise/Fall Time (see Figure 2)

660 MHz 50% duty cycle

Differential 20% to 80%

0.08

0.3

ns

Notes:

11. V

(AC) is the minimum differential HSTL input voltage swing required to maintain AC characteristics including tkpd and device-to-device skew.

12.50% duty cycle; standard load; differential operation.

13.For 3.3V supplies. Jitter measured differentially using an Agilent 8133A Pulse Generator with an 8500A LeCroy Wavemaster Oscilloscope using at least 10,000

data points.

14.Output pulse skew is the absolute difference of the propagation delay times: | t

PLH

– t

PHL

|.

相关PDF资料 |

PDF描述 |

|---|---|

| CY2DP314OXIT | 1-2 COMPOSITE VIDEO SPLITTER |

| CY2DP314 | 1 of 2:4 Differential Clock/Data Fanout Buffer |

| CY2DP818ZC | CRIMP SHELLS DB9 MALE |

| CY2DP818ZCT | Computers; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No RoHS Compliant: No |

| CY2DP818ZI | COMPUTER ACCESSORY |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY2DP314OXIT | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:1:4 Differential Clock/Data Fanout Buffer |

| CY2DP814 | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:1:4 Clock Fanout Buffer |

| CY2DP814_05 | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:ComLink⑩ Series |

| CY2DP814_08 | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:1:4 Clock Fanout Buffer |

| CY2DP814SC | 制造商:Cypress Semiconductor 功能描述: |

发布紧急采购,3分钟左右您将得到回复。