- 您现在的位置:买卖IC网 > PDF目录298975 > CY37384VP160-200UXC (Cypress Semiconductor Corp.) BATTERY SLA 6V 12AH .250 TERM PDF资料下载

参数资料

| 型号: | CY37384VP160-200UXC |

| 厂商: | Cypress Semiconductor Corp. |

| 英文描述: | BATTERY SLA 6V 12AH .250 TERM |

| 中文描述: | 为5V,3.3V,ISRTM高性能的CPLD |

| 文件页数: | 62/64页 |

| 文件大小: | 1798K |

| 代理商: | CY37384VP160-200UXC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页当前第62页第63页第64页

Ultra37000 CPLD Family

Document #: 38-03007 Rev. *D

Page 7 of 64

JTAG and PCI Standards

PCI Compliance

5V operation of the Ultra37000 is fully compliant with the PCI

Local Bus Specification published by the PCI Special Interest

Group. The 3.3V products meet all PCI requirements except

for the output 3.3V clamp, which is in direct conflict with 5V

tolerance. The Ultra37000 family’s simple and predictable

timing model ensures compliance with the PCI AC specifica-

tions independent of the design.

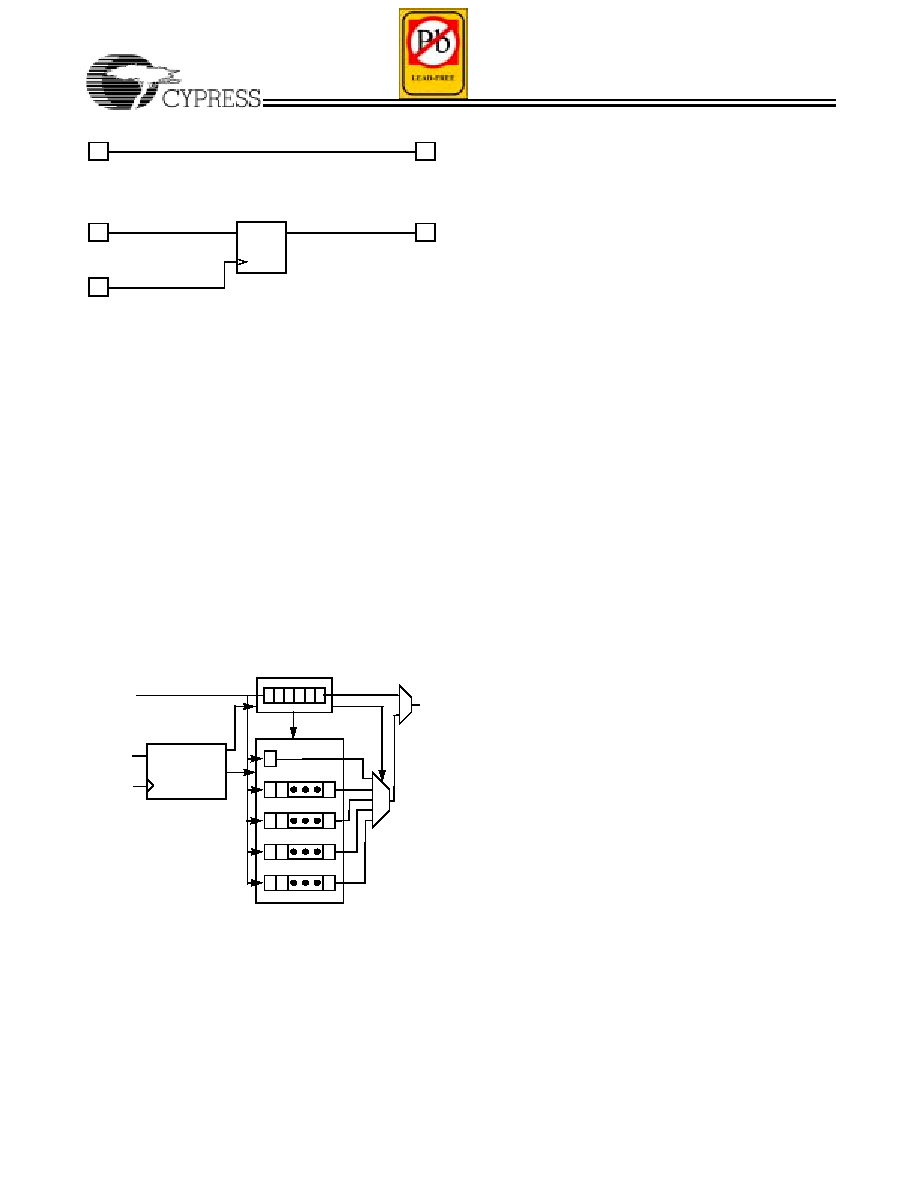

IEEE 1149.1-compliant JTAG

The Ultra37000 family has an IEEE 1149.1 JTAG interface for

both Boundary Scan and ISR.

Boundary Scan

The Ultra37000 family supports Bypass, Sample/Preload,

Extest, Idcode, and Usercode boundary scan instructions. The

JTAG interface is shown in Figure 6.

In-System Reprogramming (ISR)

In-System Reprogramming is the combination of the capability

to program or reprogram a device on-board, and the ability to

support design changes without changing the system timing

or device pinout. This combination means design changes

during debug or field upgrades do not cause board respins.

The Ultra37000 family implements ISR by providing a JTAG

compliant interface for on-board programming, robust routing

resources for pinout flexibility, and a simple timing model for

consistent system performance.

Development Software Support

Warp

Warp is a state-of-the-art compiler and complete CPLD design

tool. For design entry, Warp provides an IEEE-STD-1076/1164

VHDL text editor, an IEEE-STD-1364 Verilog text editor, and a

graphical finite state machine editor. It provides optimized

synthesis and fitting by replacing basic circuits with ones

pre-optimized for the target device, by implementing logic in

unused memory and by perfect communication between fitting

and synthesis. To facilitate design and debugging, Warp

provides graphical timing simulation and analysis.

Warp Professional

Warp Professional contains several additional features. It

provides an extra method of design entry with its graphical

block diagram editor. It allows up to 5 ms timing simulation

instead of only 2 ms. It allows comparison of waveforms before

and after design changes.

Warp Enterprise

Warp Enterprise provides even more features. It provides

unlimited timing simulation and source-level behavioral

simulation as well as a debugger. It has the ability to generate

graphical HDL blocks from HDL text. It can even generate

testbenches.

Warp is available for PC and UNIX platforms. Some features

are not available in the UNIX version. For further information

see the Warp for PC, Warp for UNIX, Warp Professional and

Warp Enterprise data sheets on Cypress’s web site

(www.cypress.com).

Third-Party Software

Although Warp is a complete CPLD development tool on its

own, it interfaces with nearly every third party EDA tool. All

major third-party software vendors provide support for the

Ultra37000 family of devices. Refer to the third-party software

data sheet or contact your local sales office for a list of

currently supported third-party vendors.

Programming

There are four programming options available for Ultra37000

devices. The first method is to use a PC with the 37000

UltraISR programming cable and software. With this method,

the ISR pins of the Ultra37000 devices are routed to a

connector at the edge of the printed circuit board. The 37000

UltraISR programming cable is then connected between the

parallel port of the PC and this connector. A simple configu-

ration file instructs the ISR software of the programming

operations to be performed on each of the Ultra37000 devices

in the system. The ISR software then automatically completes

all of the necessary data manipulations required to accomplish

the programming, reading, verifying, and other ISR functions.

For more information on the Cypress ISR Interface, see the

ISR Programming Kit data sheet (CY3700i).

The second method for programming Ultra37000 devices is on

automatic test equipment (ATE). This is accomplished through

a file created by the ISR software. Check the Cypress website

for the latest ISR software download information.

Figure 5. Timing Model for CY37128

Figure 6. JTAG Interface

COMBINATORIAL SIGNAL

REGISTERED SIGNAL

D,T,L

O

CLOCK

INPUT

OUTPUT

tS = 3.5 ns

tCO = 4.5 ns

tPD = 6.5 ns

Instruction Register

Boundary Scan

idcode

Usercode

ISR Prog.

Bypass Reg.

Data Registers

JTAG

TAP

CONTROLLER

TDO

TDI

TMS

TCK

相关PDF资料 |

PDF描述 |

|---|---|

| CY37384VP208-200UXC | BATTERY SEALED LEAD ACID 12V 3AH |

| CY37384VP208-83UXC | 5V, 3.3V, ISRTM High-Performance CPLDs |

| CY37384VP256-143YXC | 5V, 3.3V, ISRTM High-Performance CPLDs |

| CY37384VP256-154AXC | 5V, 3.3V, ISRTM High-Performance CPLDs |

| CY37384VP256-154BAXC | 5V, 3.3V, ISRTM High-Performance CPLDs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY37512P208-100NI | 制造商:Cypress Semiconductor 功能描述: |

| CY37512P208-100NXI | 功能描述:IC CPLD 512 MACROCELL 208BQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:Ultra37000™ 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| CY37512P208-125NC | 制造商:Cypress Semiconductor 功能描述:CPLD Ultra37000 Family 15K Gates 512 Macro Cells 125MHz 5V 208-Pin PQFP 制造商:Cypress Semiconductor 功能描述:CPLD Ultra37000 Family 15K Gates 512 Macro Cells 125MHz CMOS Technology 5V 208-Pin PQFP |

| CY37512P208-125NXC | 功能描述:IC CPLD 512 MACROCELL 208BQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:Ultra37000™ 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| CY37512P208-83NC | 制造商:Cypress Semiconductor 功能描述:CPLD Ultra37000 Family 15K Gates 512 Macro Cells 83MHz 5V 208-Pin PQFP |

发布紧急采购,3分钟左右您将得到回复。