- 您现在的位置:买卖IC网 > PDF目录380137 > CY39200V256-233BGI (Cypress Semiconductor Corp.) CPLDs at FPGA Densities PDF资料下载

参数资料

| 型号: | CY39200V256-233BGI |

| 厂商: | Cypress Semiconductor Corp. |

| 英文描述: | CPLDs at FPGA Densities |

| 中文描述: | CPLD器件在FPGA的密度 |

| 文件页数: | 15/86页 |

| 文件大小: | 1235K |

| 代理商: | CY39200V256-233BGI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页

Delta39K ISR

CPLD Family

Document #: 38-03039 Rev. *H

Page 15 of 86

Configuration can begin in two ways. It can be initiated by

toggling the

Reconfig

pin from LOW to HIGH, or by issuing the

appropriate IEEE STD 1149.1 JTAG instruction to the

Delta39K device via the JTAG interface. There are two IEEE

STD 1149.1 JTAG instructions that initiate configuration of the

Delta39K. The

Self Config

instruction causes the Delta39K to

(re)configure with data stored in the serial boot PROM or the

embedded FLASH memory. The

Load Config

instruction

causes the Delta39K to (re)configure according to data

provided by other sources such as a PC, automatic test

equipment (ATE), or an embedded micro-controller/processor

via the JTAG interface. For more information on configuring

Delta39K devices, refer to the application note titled

“Config-

uring Delta39K/Quantum38K”

at http://www.cypress.com.

There are two configuration options available for issuing the

IEEE STD 1149.1 JTAG instructions to the Delta39K. The first

method is to use a PC with the C3ISR programming cable and

software. With this method, the ISR pins of the Delta39K

devices in the system are routed to a connector at the edge of

the printed circuit board. The C3ISR programming cable is

then connected between the PC and this connector. A simple

configuration file instructs the ISR software of the

programming operations to be performed on the Delta39K

devices in the system. The ISR software then automatically

completes all of the necessary data manipulations required to

accomplish configuration, reading, verifying, and other ISR

functions. For more information on the Cypress ISR interface,

see the ISR Programming Kit data sheet (CY3900i).

The second configuration option for the Delta39K is to utilize

the embedded controller or processor that already exists in the

system. The Delta39K ISR software assists in this method by

converting the device HEX file into the ISR serial stream that

contains the ISR instruction information and the addresses

and data of locations to be configured. The embedded

controller then simply directs this ISR stream to the chain of

Delta39K devices to complete the desired reconfiguration or

diagnostic operations. Contact your local sales office for infor-

mation on the availability of this option.

Programming

The on-chip FLASH device of the Delta39K Self-Boot package

is programmed by issuing the appropriate IEEE STD 1149.1

JTAG instruction to the internal FLASH memory via the JTAG

interface. This can be done automatically using ISR/STAPL

software. The configuration bits are sent from a PC through

the JTAG port into the Delta39K via the C3ISR programming

cable. The data is then internally passed from Delta39K to the

on-chip FLASH. For more information on how to program the

Delta39K through ISR/STAPL, please refer to the ISR/STAPL

User Guide.

The external CPLD boot EEPROM used to store configuration

data for the Delta39K volatile package is programmed through

Cypress’s CYDH2200E CPLD Boot PROM Programming Kit

via a two-wire interface. For more information on how to

program the CPLD boot EEPROM, please refer to the data

sheet titled “

CYDH2200E CPLD Boot PROM Programming

Kit

.” For more information on the architecture and timing speci-

fication of the boot EEPROM, refer to the data sheet titled

“

512K/1Mb CPLD Boot EEPROM

” or “

2-Mbit CPLD Boot

EEPROM.

”

Third-Party Programmers

Cypress support is available on a wide variety of third-party

programmers. All major programmers (including BP Micro,

System General, Hi-Lo) support the Delta39K family.

Development Software Support

Warp

Warp

is a state-of-the-art design environment for designing

with Cypress programmable logic.

Warp

utilizes a subset of

IEEE 1076/1164 VHDL and IEEE 1364 as the Hardware

Description Language (HDL) for design entry.

Warp

accepts

VHDL or Verilog input, synthesizes and optimizes the entered

design, and outputs a configuration bitstream for the desired

Delta39K device. For simulation,

Warp

provides a graphical

waveform simulator as well as VHDL and Verilog Timing

Models.

VHDL and Verilog are open, powerful, non-proprietary

Hardware Description Languages (HDLs) that are standards

for behavioral design entry and simulation. HDL allows

designers to learn a single language that is useful for all facets

of the design process.

Third-Party Software

Cypress products are supported in a number of third-party

design entry and simulation tools. Refer to the third-party

software data sheet or contact your local sales office for a list

of currently supported third party vendors.

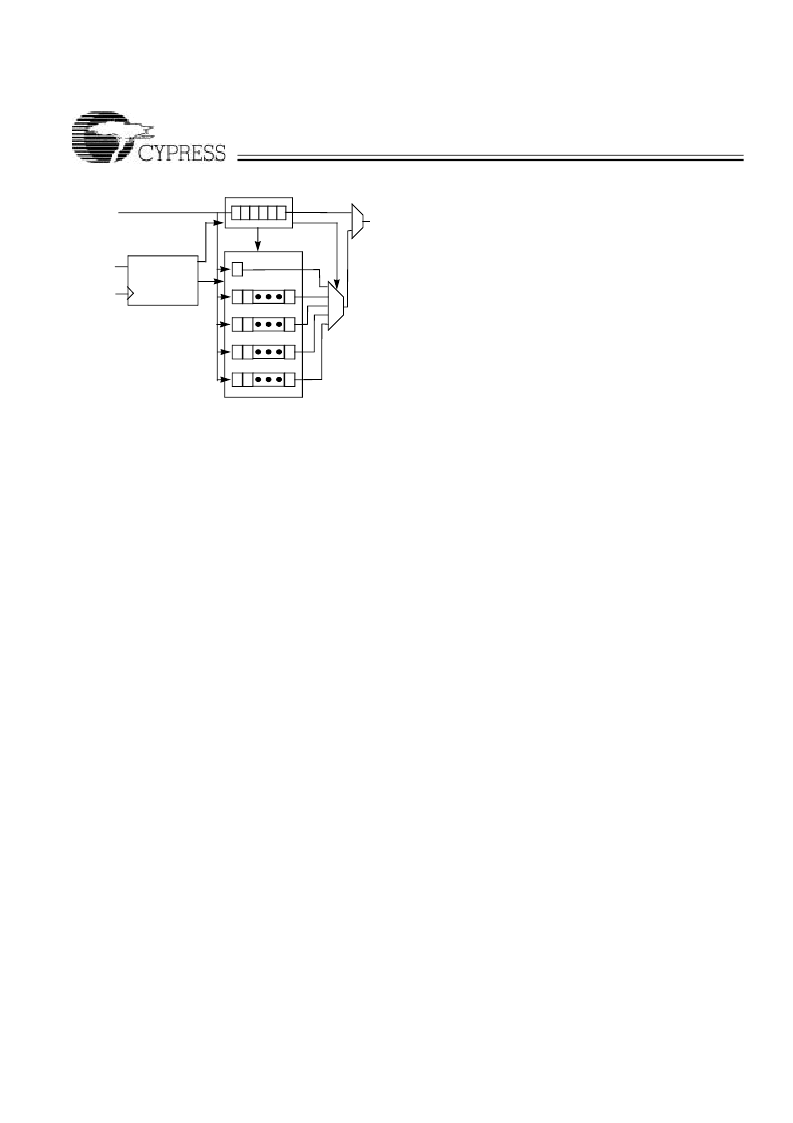

Instruction Register

Boundary Scan

idcode

Usercode

ISR Prog.

Bypass Reg.

Data Registers

JTAG

TAP

CONTROLLER

TDO

TDI

TMS

TCLK

Figure 11. JTAG Interface

相关PDF资料 |

PDF描述 |

|---|---|

| CY39200V256-233MBC | CPLDs at FPGA Densities |

| CY39200V256-233MBI | CPLDs at FPGA Densities |

| CY39200V256-233NC | CPLDs at FPGA Densities |

| CY39200V256-233NI | CPLDs at FPGA Densities |

| CY39200V256-233NTI | CPLDs at FPGA Densities |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY39200V256-233MGC | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39200V256-233MGI | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39200V256-233NTC | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39200V388-125MGC | 功能描述:IC CPLD 200K GATE 388-BGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:Delta 39K™ ISR™ 标准包装:40 系列:ispMACH® 4000C 可编程类型:系统内可编程 最大延迟时间 tpd(1):5.0ns 电压电源 - 内部:1.65 V ~ 1.95 V 逻辑元件/逻辑块数目:32 宏单元数:512 门数:- 输入/输出数:128 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:176-LQFP 供应商设备封装:176-TQFP(24x24) 包装:托盘 |

| CY39200V388-181MGC | 制造商:Cypress Semiconductor 功能描述: |

发布紧急采购,3分钟左右您将得到回复。