- 您现在的位置:买卖IC网 > PDF目录380137 > CY39200V256-233MBI (Cypress Semiconductor Corp.) CPLDs at FPGA Densities PDF资料下载

参数资料

| 型号: | CY39200V256-233MBI |

| 厂商: | Cypress Semiconductor Corp. |

| 英文描述: | CPLDs at FPGA Densities |

| 中文描述: | CPLD器件在FPGA的密度 |

| 文件页数: | 5/86页 |

| 文件大小: | 1235K |

| 代理商: | CY39200V256-233MBI |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页

Delta39K ISR

CPLD Family

Document #: 38-03039 Rev. *H

Page 5 of 86

Logic Block

The LB is the basic building block of the Delta39K architecture.

It consists of a product term array, an intelligent product-term

allocator, and 16 macrocells.

Product Term Array

Each logic block features a 72 x 83 programmable product

term array. This array accepts 36 inputs from the PIM. These

inputs originate from device pins and macrocell feedbacks as

well as cluster memory and channel memory feedbacks.

Active LOW and active HIGH versions of each of these inputs

are generated to create the full 72-input field. The 83 product

terms in the array can be created from any of the 72 inputs.

Of the 83 product terms, 80 are for general-purpose use for

the 16 macrocells in the logic block. Two of the remaining three

product terms in the logic block are used as asynchronous set

and asynchronous reset product terms. The final product term

is the Product Term clock (PTCLK) and is shared by all 16

macrocells within a logic block.

Product Term Allocator

Through the product term allocator,

Warp

software automati-

cally distributes the 80 product terms as needed among the 16

macrocells in the logic block. The product term allocator

provides two important capabilities without affecting perfor-

mance: product term steering and product term sharing.

Product Term Steering

Product term steering is the process of assigning product

terms to macrocells as needed. For example, if one macrocell

requires ten product terms while another needs just three, the

product term allocator will “steer” ten product terms to one

macrocell and three to the other. On Delta39K devices,

product terms are steered on an individual basis. Any number

between 1 and 16 product terms can be steered to any

macrocell.

Product Term Sharing

Product term sharing is the process of using the same product

term among multiple macrocells. For example, if more than

one function has one or more product terms in its equation that

are common to other functions, those product terms are only

programmed once. The Delta39K product term allocator

allows sharing across groups of four macrocells in a variable

fashion. The software automatically takes advantage of this

capability so that the user does not have to intervene.

Note that neither product term sharing nor product term

steering have any effect on the speed of the product. All

steering and sharing configurations have been incorporated in

the timing specifications for the Delta39K devices.

.

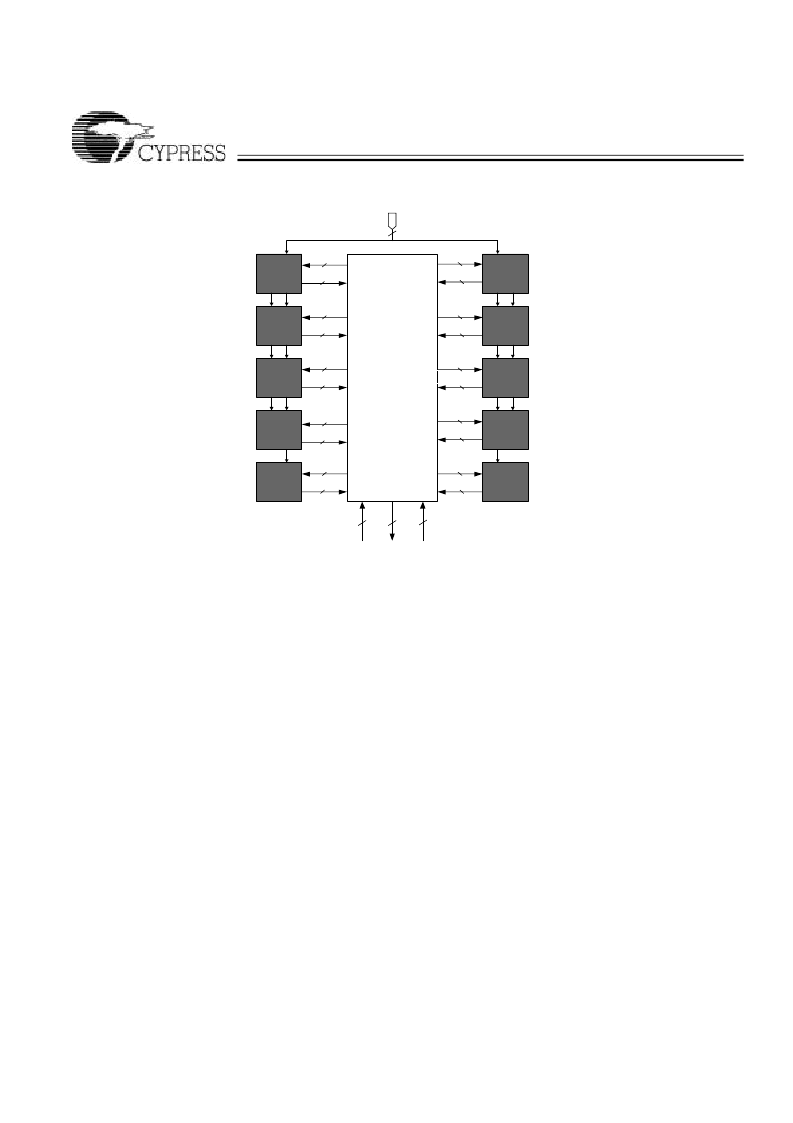

Logic

Block

0

Logic

Block

1

Logic

Block

3

Logic

Block

2

Cluster

Memory

0

PIM

Logic

Block

7

Logic

Block

6

Logic

Block

4

Logic

Block

5

Cluster

Memory

1

64 Inputs From

Horizontal Routing

Channel

64 Inputs From

Vertical Routing

Channel

144 Outputs to

Horizontal and Vertical

cluster-to-channel PIMs

Clock Inputs

GCLK[3:0]

C

C

C

C

C

C

CC = Carry Chain

16

36

16

36

16

36

16

36

16

36

16

36

16

36

8

25

8

25

4

16

36

Figure 3. Delta39K Logic Block Cluster Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| CY39200V256-233NC | CPLDs at FPGA Densities |

| CY39200V256-233NI | CPLDs at FPGA Densities |

| CY39200V256-233NTI | CPLDs at FPGA Densities |

| CY39200V256-83BBC | CPLDs at FPGA Densities |

| CY39200V256-83BBI | CPLDs at FPGA Densities |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY39200V256-233MGC | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39200V256-233MGI | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39200V256-233NTC | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39200V388-125MGC | 功能描述:IC CPLD 200K GATE 388-BGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:Delta 39K™ ISR™ 标准包装:40 系列:ispMACH® 4000C 可编程类型:系统内可编程 最大延迟时间 tpd(1):5.0ns 电压电源 - 内部:1.65 V ~ 1.95 V 逻辑元件/逻辑块数目:32 宏单元数:512 门数:- 输入/输出数:128 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:176-LQFP 供应商设备封装:176-TQFP(24x24) 包装:托盘 |

| CY39200V388-181MGC | 制造商:Cypress Semiconductor 功能描述: |

发布紧急采购,3分钟左右您将得到回复。