- 您现在的位置:买卖IC网 > PDF目录295354 > CY7C0851AV-133BBC (CYPRESS SEMICONDUCTOR CORP) FLEx36™ 3.3V 32K/64K/128K/256K x 36 Synchronous Dual-Port RAM PDF资料下载

参数资料

| 型号: | CY7C0851AV-133BBC |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | SRAM |

| 英文描述: | FLEx36™ 3.3V 32K/64K/128K/256K x 36 Synchronous Dual-Port RAM |

| 中文描述: | 64K X 36 DUAL-PORT SRAM, 4 ns, PBGA172 |

| 封装: | 15 X 15 MM, 1.25 MM HEIGHT, 1 MM PITCH, FBGA-172 |

| 文件页数: | 29/32页 |

| 文件大小: | 971K |

| 代理商: | CY7C0851AV-133BBC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页

CY7C0850AV, CY7C0851AV

CY7C0852AV, CY7C0853AV

Document #: 38-06070 Rev. *H

Page 6 of 32

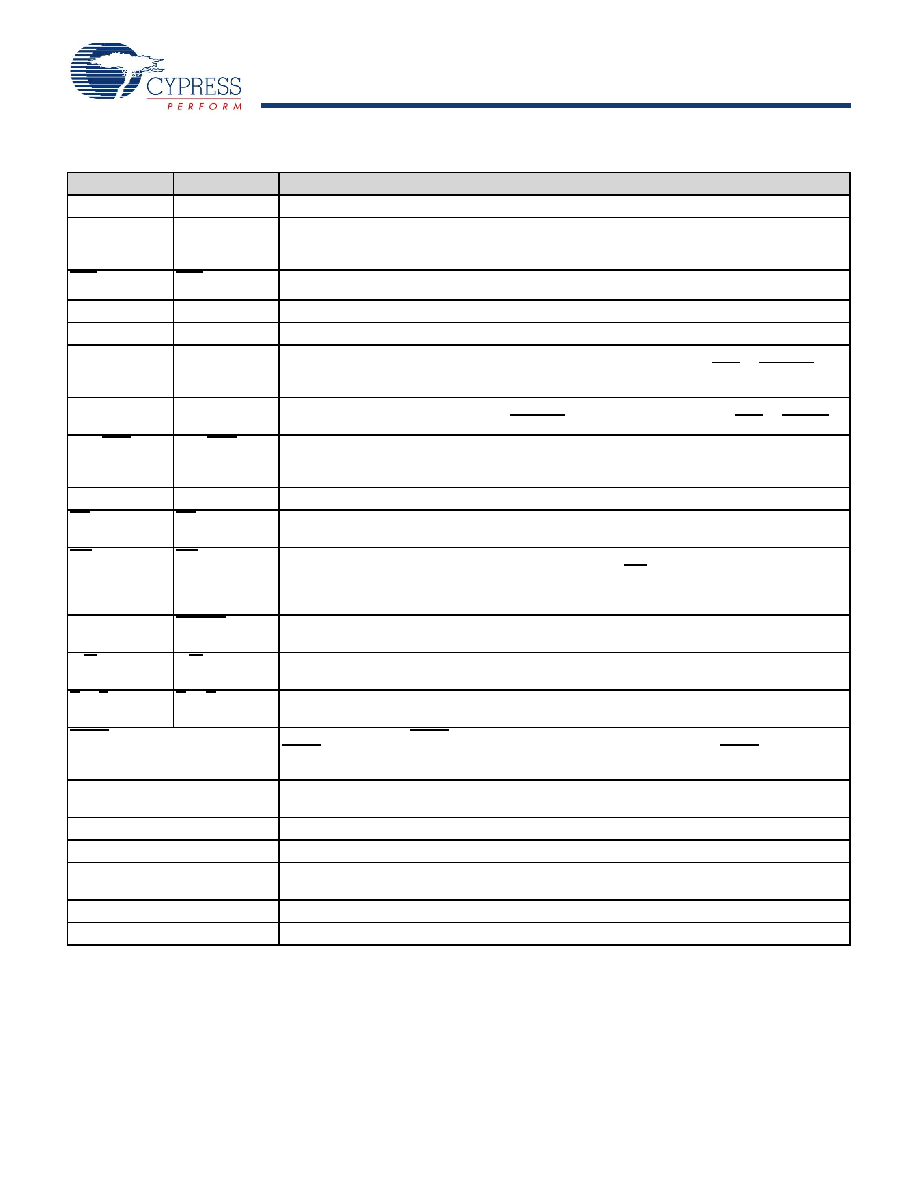

Pin Definitions

Left Port

Right Port

Description

Address Inputs.

ADSL[3]

ADSR[3]

Address Strobe Input. Used as an address qualifier. This signal should be asserted LOW for

the part using the externally supplied address on the address pins and for loading this address

into the burst address counter.

CE0L[3]

CE0R[3]

Active LOW Chip Enable Input.

CE1L[3]

CE1R[3]

Active HIGH Chip Enable Input.

CLKL

CLKR

Clock Signal. Maximum clock input rate is fMAX.

CNTENL[3]

CNTENR[3]

Counter Enable Input. Asserting this signal LOW increments the burst address counter of its

respective port on each rising edge of CLK. The increment is disabled if ADS or CNTRST are

asserted LOW.

CNTRSTL[3]

CNTRSTR[3]

Counter Reset Input. Asserting this signal LOW resets to zero the unmasked portion of the burst

address counter of its respective port. CNTRST is not disabled by asserting ADS or CNTEN.

CNT/MSKL[3]

CNT/MSKR[3]

Address Counter Mask Register Enable Input. Asserting this signal LOW enables access to

the mask register. When tied HIGH, the mask register is not accessible and the address counter

operations are enabled based on the status of the counter control signals.

DQ0L–DQ35L

DQ0R–DQ35R

Data Bus Input/Output.

OEL

OER

Output Enable Input. This asynchronous signal must be asserted LOW to enable the DQ data

pins during Read operations.

INTLINTR

Mailbox Interrupt Flag Output. The mailbox permits communications between ports. The upper

two memory locations can be used for message passing. INTL is asserted LOW when the right

port writes to the mailbox location of the left port, and vice versa. An interrupt to a port is

deasserted HIGH when it reads the contents of its mailbox.

CNTINTL[3]

CNTINTR[3]

Counter Interrupt Output. This pin is asserted LOW when the unmasked portion of the counter

is incremented to all “1s.”

R/WL

R/WR

Read/Write Enable Input. Assert this pin LOW to write to, or HIGH to Read from the dual port

memory array.

B0L–B3L

B0R–B3R

Byte Select Inputs. Asserting these signals enables Read and Write operations to the corre-

sponding bytes of the memory array.

MRST

Master Reset Input. MRST is an asynchronous input signal and affects both ports. Asserting

MRST LOW performs all of the reset functions as described in the text. A MRST operation is

required at power up.

TMS

JTAG Test Mode Select Input. It controls the advance of JTAG TAP state machine. State

machine transitions occur on the rising edge of TCK.

TDI

JTAG Test Data Input. Data on the TDI input is shifted serially into selected registers.

TCK

JTAG Test Clock Input.

TDO

JTAG Test Data Output. TDO transitions occur on the falling edge of TCK. TDO is normally

three-stated except when captured data is shifted out of the JTAG TAP.

VSS

Ground Inputs.

VDD

Power Inputs.

Note

3. These pins are not available for CY7C0853AV device.

相关PDF资料 |

PDF描述 |

|---|---|

| CY7C0851AV-167AXC | FLEx36™ 3.3V 32K/64K/128K/256K x 36 Synchronous Dual-Port RAM |

| CY7C0851AV-167BBC | FLEx36™ 3.3V 32K/64K/128K/256K x 36 Synchronous Dual-Port RAM |

| CY7C0852AV-133BBC | FLEx36™ 3.3V 32K/64K/128K/256K x 36 Synchronous Dual-Port RAM |

| CY7C0851AV-133AXI | FLEx36™ 3.3V 32K/64K/128K/256K x 36 Synchronous Dual-Port RAM |

| CY7C0851AV-133BBI | FLEx36™ 3.3V 32K/64K/128K/256K x 36 Synchronous Dual-Port RAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY7C0851AV-133BBI | 功能描述:静态随机存取存储器 2MB (64Kx36) 3.3v 133MHz Synch 静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| CY7C0851AV-167AC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC DUAL 3.3V 2.25MBIT 64KX36 4NS 176TQFP - Trays |

| CY7C0851AV-167AXC | 功能描述:静态随机存取存储器 3.3V, 64Kx36 Sync Dual Port RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| CY7C0851AV-167BBC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC DUAL 3.3V 2.25MBIT 64KX36 4NS 172FBGA - Trays 制造商:Rochester Electronics LLC 功能描述: |

| CY7C0851AV-167BBXC | 功能描述:静态随机存取存储器 2MB (64Kx36) 3.3v 167MHz Sync 静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。