- 您现在的位置:买卖IC网 > PDF目录295354 > CY7C09099V-7AI (CYPRESS SEMICONDUCTOR CORP) 3.3V 32K/64K/128K x 8/9 Synchronous Dual-Port Static RAM PDF资料下载

参数资料

| 型号: | CY7C09099V-7AI |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | SRAM |

| 英文描述: | 3.3V 32K/64K/128K x 8/9 Synchronous Dual-Port Static RAM |

| 中文描述: | 128K X 8 DUAL-PORT SRAM, 18 ns, PQFP100 |

| 封装: | ROHS COMPLIANT, PLASTIC, MS-026, TQFP-100 |

| 文件页数: | 15/20页 |

| 文件大小: | 599K |

| 代理商: | CY7C09099V-7AI |

CY7C09079V/89V/99V

CY7C09179V/89V/99V

Document #: 38-06043 Rev. *E

Page 4 of 20

Notes

8. This pin is NC for CY7C09179V.

9. This pin is NC for CY7C09179V and CY7C09189V

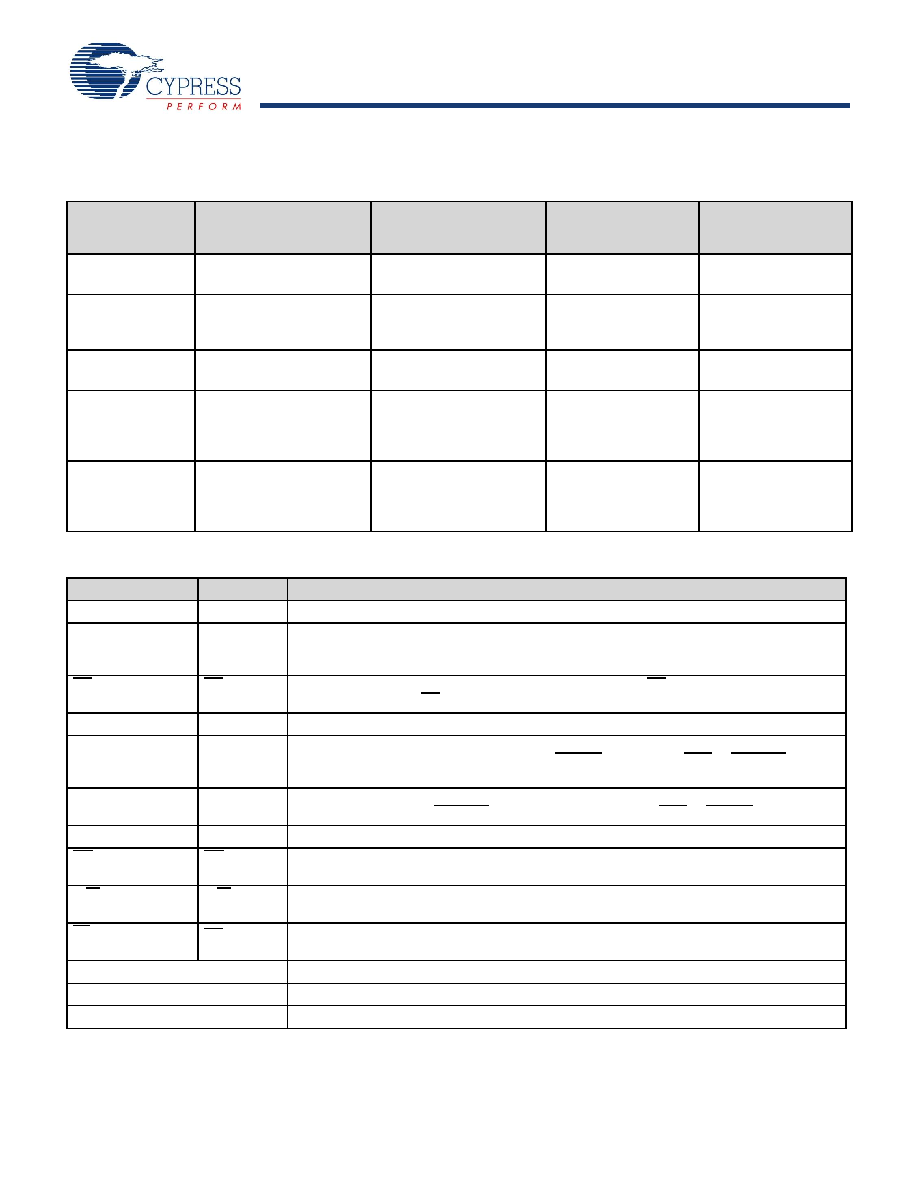

Selection Guide

Description

CY7C09079V/89V/99V

CY7C09179V/89V/99V-6[1]

CY7C09079V/89V/99V

CY7C09179V/89V/99V-7[1]

CY7C09079V/89V/99V

CY7C09179V/89V/99V

-9

CY7C09079V/89V/99V

CY7C09179V/89V/99V

-12

fMAX2 (MHz)

(Pipelined)

100

83

67

50

Max. Access Time

(ns) (Clock to Data,

Pipelined)

6.5

7.5

9

12

Typical Operating

Current ICC (mA)

175

155

135

115

Typical Standby

Current for ISB1

(mA) (Both Ports

TTL Level)

25

20

Typical Standby

Current for ISB3

(

A) (Both Ports

CMOS Level)

10

A

10

A10 A

10

A

Pin Definitions

Left Port

Right Port

Description

A0L–A16L

A0R–A16R

Address Inputs (A0–A14 for 32K; A0–A15 for 64K; and A0–A16 for 128K devices).

ADSL

ADSR

Address Strobe Input. Used as an address qualifier. This signal should be asserted LOW to

access the part using an externally supplied address. Asserting this signal LOW also loads

the burst counter with the address present on the address pins.

CE0L,CE1L

CE0R,CE1R

Chip Enable Input. To select either the left or right port, both CE0 AND CE1 must be asserted

to their active states (CE0 VIL and CE1 VIH).

CLKL

CLKR

Clock Signal. This input can be free running or strobed. Maximum clock input rate is fMAX.

CNTENL

CNTENR

Counter Enable Input. Asserting this signal LOW increments the burst address counter of its

respective port on each rising edge of CLK. CNTEN is disabled if ADS or CNTRST are

asserted LOW.

CNTRSTL

CNTRSTR

Counter Reset Input. Asserting this signal LOW resets the burst address counter of its

respective port to zero. CNTRST is not disabled by asserting ADS or CNTEN.

I/O0L–I/O8L

I/O0R–I/O8R

Data Bus Input/Output (I/O0–I/O7 for x8 devices; I/O0–I/O8 for x9 devices).

OEL

OER

Output Enable Input. This signal must be asserted LOW to enable the I/O data pins during

read operations.

R/WL

R/WR

Read/Write Enable Input. This signal is asserted LOW to write to the dual port memory array.

For read operations, assert this pin HIGH.

FT/PIPEL

FT/PIPER

Flow-Through/Pipelined Select Input. For flow-through mode operation, assert this pin LOW.

For pipelined mode operation, assert this pin HIGH.

GND

Ground Input.

NC

No Connect.

VCC

Power Input.

相关PDF资料 |

PDF描述 |

|---|---|

| CY7C09099V-12AXC | 3.3V 32K/64K/128K x 8/9 Synchronous Dual-Port Static RAM |

| CY7C09099V-7AXI | 3.3V 32K/64K/128K x 8/9 Synchronous Dual-Port Static RAM |

| CY7C09179V-12AXC | 3.3V 32K/64K/128K x 8/9 Synchronous Dual-Port Static RAM |

| CY7C09179V-6AXC | 3.3V 32K/64K/128K x 8/9 Synchronous Dual-Port Static RAM |

| CY7C09199V-9AXC | 3.3V 32K/64K/128K x 8/9 Synchronous Dual-Port Static RAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY7C09099V-7AXI | 功能描述:静态随机存取存储器 3.3V 128Kx8 IND Sync Dual Port 静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| CY7C09099V-9AC | 制造商:Cypress Semiconductor 功能描述:SRAM Chip Sync Dual 3.3V 1M-Bit 128K x 8 20ns/9ns 100-Pin TQFP |

| CY7C09099V-9AI | 制造商:Cypress Semiconductor 功能描述:SRAM Chip Sync Dual 3.3V 1M-Bit 128K x 8 20ns/9ns 100-Pin TQFP |

| CY7C09159AV-12AC | 功能描述:IC SRAM 72KBIT 12NS 100LQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI |

| CY7C09159AV-12AXC | 功能描述:静态随机存取存储器 3.3V 8Kx9 COM Sync Dual Port 静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。