- 您现在的位置:买卖IC网 > PDF目录223638 > CY7C344B-15JIT (CYPRESS SEMICONDUCTOR CORP) OT PLD, 15 ns, PQCC28 PDF资料下载

参数资料

| 型号: | CY7C344B-15JIT |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | OT PLD, 15 ns, PQCC28 |

| 封装: | PLASTIC, LCC-28 |

| 文件页数: | 8/12页 |

| 文件大小: | 394K |

| 代理商: | CY7C344B-15JIT |

USE ULTRA37000 FOR

ALL NEW DESIGNS

CY7C344B

Document #: 38-03036 Rev. *D

Page 5 of 12

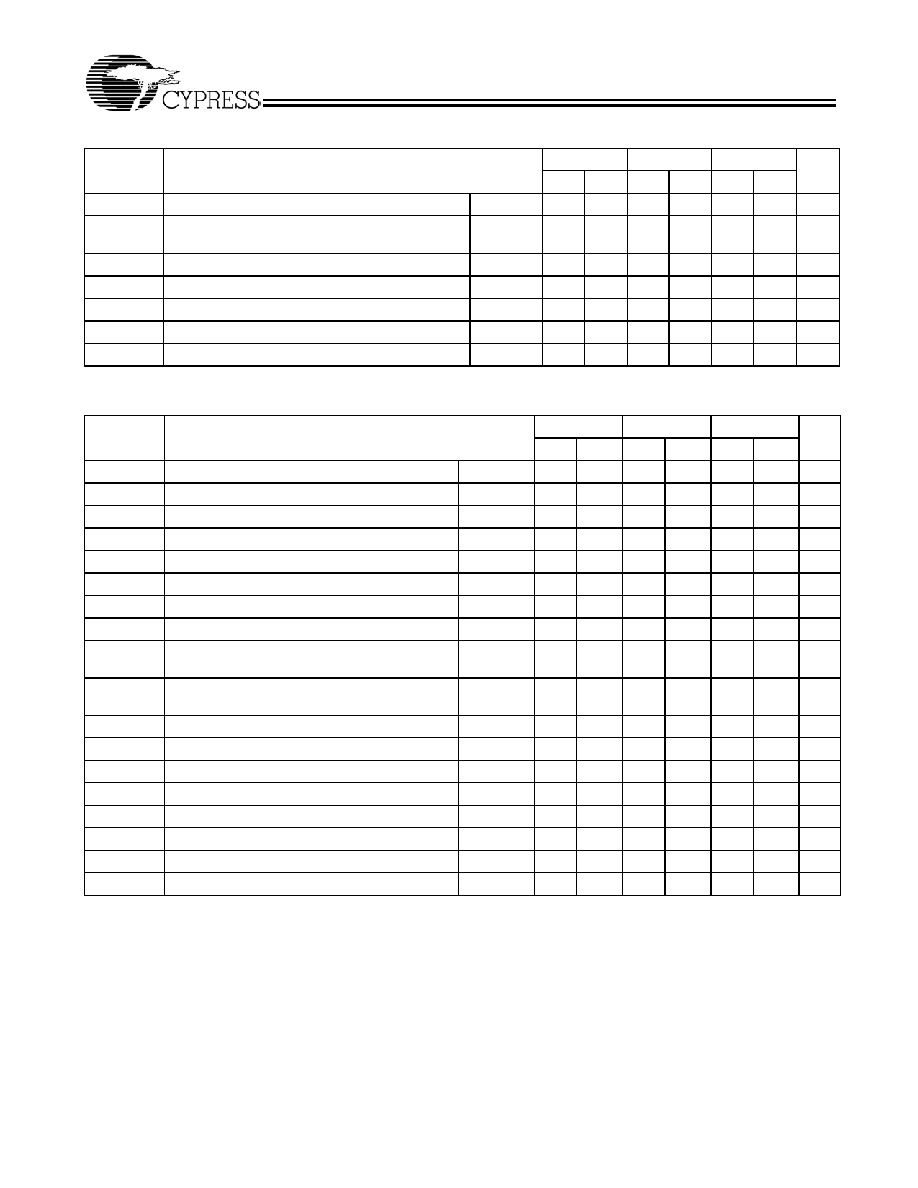

External Asynchronous Switching Characteristics Over Operating Range

7C344B-15

7C344B-20

7C344B-25

Parameter

Description

Min. Max. Min. Max. Min. Max. Unit

tACO1

Asynchronous Clock Input to Output Delay[5]

Com’l/Ind

15

18

22

ns

tAS1

Dedicated Input or Feedback Set-Up Time to

Asynchronous Clock Input

Com’l/Ind

5

6

8

ns

tAH

Input Hold Time from Asynchronous Clock Input

Com’l/Ind

5

6

8

ns

tAWH

Asynchronous Clock Input HIGH Time[8]

Com’l/Ind

6

7

9

ns

tAWL

Asynchronous Clock Input LOW Time[8]

Com’l/Ind

7

9

11

ns

tACNT

Minimum Internal Array Clock Frequency

Com’l/Ind

13

16

20

ns

fACNT

Maximum Internal Array Clock Frequency[7]

Com’l/Ind

76.9

62.5

50

MHz

Typical Internal Switching Characteristics Over Operating Range

7C344B-15

7C344B-20

7C344B-25

Parameter

Description

Min.

Max.

Min.

Max.

Min.

Max.

Unit

tIN

Dedicated Input Pad and Buffer Delay

Com’l/Ind

3

5

7

ns

tIO

I/O Input Pad and Buffer Delay

Com’l/Ind

3

5

7

ns

tEXP

Expander Array Delay

Com’l/Ind

8

10

15

ns

tLAD

Logic Array Data Delay

Com’l/Ind

7

10

13

ns

tLAC

Logic Array Control Delay

Com’l/Ind

4

ns

tOD

Output Buffer and Pad Delay[5]

Com’l/Ind

4

ns

tZX

Output Buffer Enable Delay[5]

Com’l /Ind

7

ns

tXZ

Output Buffer Disable Delay[5]

Com’l/Ind

7

ns

tRSU

Register Set-Up Time Relative to Clock Signal

at Register

Com’l/Ind

4

5

ns

tRH

Register Hold Time Relative to Clock Signal at

Register

Com’l/Ind

5

8

10

ns

tLATCH

Flow-Through Latch Delay

Com’l/Ind

1

ns

tRD

Register Delay

Com’l/Ind

1

ns

tCOMB

Transparent Mode Delay

Com’l/Ind

1

ns

tIC

Asynchronous Clock Logic Delay

Com’l/Ind

7

8

10

ns

tICS

Synchronous Clock Delay

Com’l/Ind

2

3

ns

tFD

Feedback Delay

Com’l/Ind

1

ns

tPRE

Asynchronous Register Preset Time

Com’l/Ind

5

6

9

ns

tCLR

Asynchronous Register Clear Time

Com’l/Ind

5

6

9

ns

Note:

8. This parameter is measured with a positive-edge-triggered clock at the register. For the negative-edge clocking, the tACH and tACL parameter must be swapped.

相关PDF资料 |

PDF描述 |

|---|---|

| CY7C344B-15PC | OT PLD, 15 ns, PDIP28 |

| CY7C344B-15PI | OT PLD, 15 ns, PDIP28 |

| CY7C344B-20PC | OT PLD, 20 ns, PDIP28 |

| CY7C344B-20PI | OT PLD, 20 ns, PDIP28 |

| CY7C344B-25PC | OT PLD, 25 ns, PDIP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY7C344B-15WC | 制造商:QP Semiconductor 功能描述: 制造商:QP Semiconductor 功能描述:7C344B CYP DIE 15NS-CWDIP |

| CY7C344B-20HC | 制造商:Cypress Semiconductor 功能描述:CPLD MAX? Family 600 Gates 32 Macro Cells 62.5MHz 0.65um Technology 5V 28-Pin Windowed LCC |

| CY7C344B-20WC | 制造商:Cypress Semiconductor 功能描述:CPLD MAX? Family 600 Gates 32 Macro Cells 62.5MHz 0.65um Technology 5V 28-Pin Windowed CDIP |

| CY7C346-25JC | 制造商:Cypress Semiconductor 功能描述:CPLD MAX? Family 2.5K Gates 128 Macro Cells 0.8um Technology 5V 84-Pin PLCC |

| CY7C346-35HI | 制造商:QP Semiconductor 功能描述:CYP BIN-7C346A 35NS-LCC-I/T |

发布紧急采购,3分钟左右您将得到回复。