- 您现在的位置:买卖IC网 > PDF目录373038 > DAC1208D750HN (NXP SEMICONDUCTORS) Dual 12-bit DAC; up to 750 Msps; 2×, 4× or 8× interpolating PDF资料下载

参数资料

| 型号: | DAC1208D750HN |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | DAC |

| 英文描述: | Dual 12-bit DAC; up to 750 Msps; 2×, 4× or 8× interpolating |

| 中文描述: | SERIAL INPUT LOADING, 0.02 us SETTLING TIME, 12-BIT DAC, PQCC64 |

| 封装: | 9 X 9 MM, 0.85 MM HEIGHT, PLASTIC, SOT804-3, VQFN-64 |

| 文件页数: | 13/98页 |

| 文件大小: | 554K |

| 代理商: | DAC1208D750HN |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页

DAC1208D750

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2010. All rights reserved.

Product data sheet

Rev. 2 — 6 December 2010

13 of 98

NXP Semiconductors

DAC1208D750

2

×

, 4

×

or 8

×

interpolating DAC with JESD204A

10.2.1

Lane input

Each lane is CML compliant. It is terminated to a common voltage with an integrated 50

Ω

resistor.

The common-mode voltage is programmable by the SET_VCM_VOLTAGE register as

shown in

Table 75 on page 55

.

DC coupling is only possible if both the DAC and the transmitter have the same

common-mode voltage. If this is not the case AC coupling is required.

The deserializer performs the incoming data clock recovery and also the serial-to-parallel

conversion. Therefore, each lane includes its own PLL that must first lock.

The clock alignment module transfers the data from the regenerated clock to the frame

clock domain. The frequency of both clocks is the same but the phase relationship

between the clocks is unknown.

10.2.2

Sync and word align

As stated in JESD204A, the transmitter and the receiver first have to synchronize. This is

achieved through SYNC_OUT signals and a sync pattern (K28.5 symbol). The receiver

(i.e. DAC1208D750) first drives its SYNC_OUT outputs. The sync pattern is continuously

sent until the receiver deasserts the SYNC_OUT signal.

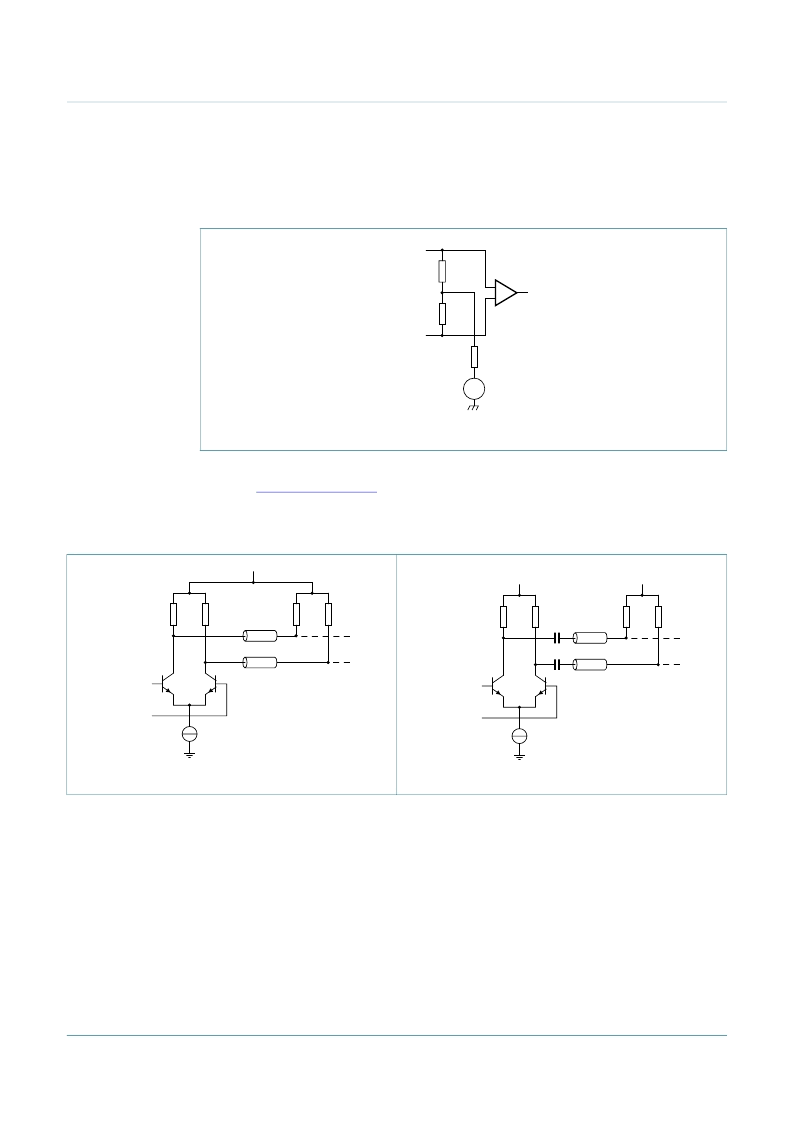

Fig 4.

Lane input termination

V

tt

001aak166

50

Ω

Ztt

50

Ω

Vin_p

Vin_n

Fig 5.

DC coupling

Fig 6.

AC coupling

001aak162

50

Ω

50

Ω

50

Ω

50

Ω

Zdiff = 100

Ω

data in +

data in

001aak163

50

Ω

50

Ω

50

Ω

50

Ω

Zdiff = 100

Ω

V

DD1

V

DD2

data in +

data in

相关PDF资料 |

PDF描述 |

|---|---|

| DAC1208D750HN | Dual 12-bit DAC; up to 750 Msps; 2×, 4× or 8× interpolating |

| DL-5538S-C550-SB | 1270 nm ~ 1610 nm DFB LD MODULES 2.5 Gbps CWDM MQW-DFB LD RECEPTACLE |

| DL-5538S-C450-FB | 1270 nm ~ 1610 nm DFB LD MODULES 2.5 Gbps CWDM MQW-DFB LD RECEPTACLE |

| DL-5538S-C450-S | 1270 nm ~ 1610 nm DFB LD MODULES 2.5 Gbps CWDM MQW-DFB LD RECEPTACLE |

| DL-5538S-C450-SB | 1270 nm ~ 1610 nm DFB LD MODULES 2.5 Gbps CWDM MQW-DFB LD RECEPTACLE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DAC1208D750HN/C1,5 | 功能描述:数模转换器- DAC DL 12BIT DAC 750MSPS 2X 4X OR 8X INT RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC1208D750HN-C1 | 功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC1208D750HN-C18 | 功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC1208LCD | 制造商:未知厂家 制造商全称:未知厂家 功能描述:12-Bit Digital-to-Analog Converter |

发布紧急采购,3分钟左右您将得到回复。