- 您现在的位置:买卖IC网 > PDF目录19024 > DC1620A-K (Linear Technology)BOARD DEMO 40MSPS LTC2141-14 PDF资料下载

参数资料

| 型号: | DC1620A-K |

| 厂商: | Linear Technology |

| 文件页数: | 15/38页 |

| 文件大小: | 0K |

| 描述: | BOARD DEMO 40MSPS LTC2141-14 |

| 软件下载: | QuikEval II System |

| 设计资源: | DC1620A Design Files DC1620A Schematic |

| 标准包装: | 1 |

| 系列: | * |

| 相关产品: | DC890B-ND - BOARD USB DATA COLLECTION |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页

LTC2142-14/

LTC2141-14/LTC2140-14

22

21421014fa

APPLICATIONS INFORMATION

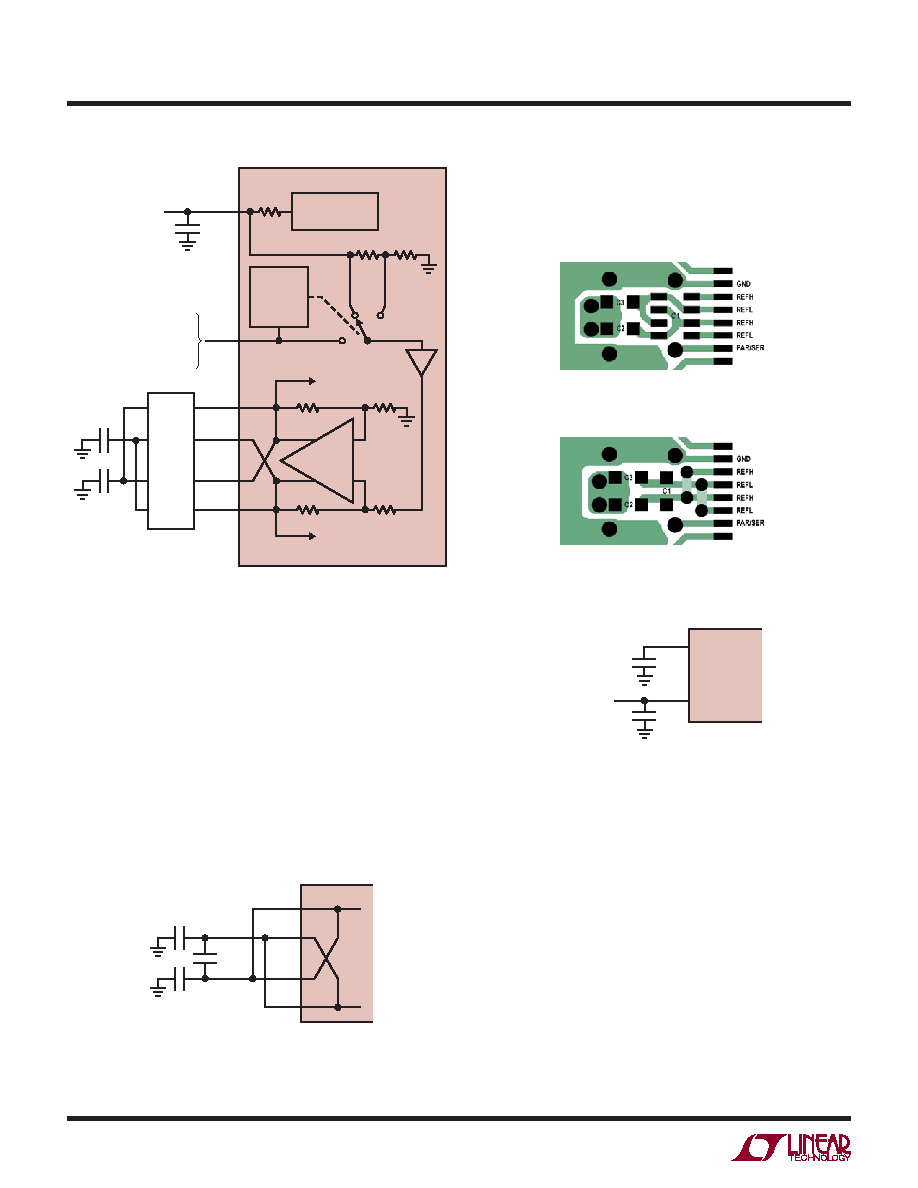

VREF

REFH

SENSE

C1

TIE TO VDD FOR 2V RANGE;

TIE TO GND FOR 1V RANGE;

SENSE FOR

0.625V < VSENSE < 1.300V

1.25V

REFL

INTERNAL ADC

HIGH REFERENCE

BUFFER

21421014 F08a

LTC2142

5Ω

0.8x

DIFF AMP

INTERNAL ADC

LOW REFERENCE

C1: 2.2μF LOW INDUCTANCE

INTERDIGITATED CAPACITOR

TDK CLLE1AX7S0G225M

MURATA LLA219C70G225M

AVX W2L14Z225M

OR EQUIVALENT

1.25V BANDGAP

REFERENCE

0.625V

RANGE

DETECT

AND

CONTROL

2.2μF

C2

0.1μF

C3

0.1μF

+

–

+

Figure 8a. Reference Circuit

SENSE

1.25V

EXTERNAL

REFERENCE

2.2μF

1μF

VREF

21421014 F09

LTC2142

Figure 9. Using an External 1.25V Reference

REFH

REFL

21421014 F08b

LTC2142

CAPACITORS ARE 0402 PACKAGE SIZE

C3

0.1μF

C1

2.2μF

C2

0.1μF

Figure 8b. Alternative REFH/REFL Bypass Circuit

Figure 8c. Recommended Layout for the REFH/REFL

Bypass Circuit in Figure 8a

Alternatively C1 can be replaced by a standard 2.2μF

capacitor between REFH and REFL (see Figure 8b). The

capacitors should be as close to the pins as possible (not

on the back side of the circuit board).

Figure 8c and Figure 8d show the recommended circuit

board layout for the REFH/REFL bypass capacitors. Note

that in Figure 8c, every pin of the interdigitated capacitor

(C1) is connected since the pins are not internally connected

in some vendors’ capacitors. In Figure 8d the REFH and

Figure 8d. Recommended Layout for the REFH/REFL

Bypass Circuit in Figure 8b

Encode Inputs

The signal quality of the encode inputs strongly affects

the A/D noise performance. The encode inputs should

be treated as analog signals – do not route them next to

digital traces on the circuit board. There are two modes

of operation for the encode inputs: the differential encode

mode (Figure 10), and the single-ended encode mode

(Figure 11).

The differential encode mode is recommended for si-

nusoidal, PECL, or LVDS encode inputs (Figure 12 and

Figure 13). The encode inputs are internally biased to 1.2V

through 10k equivalent resistance. The encode inputs can

be taken above VDD (up to 3.6V), and the common mode

range is from 1.1V to 1.6V. In the differential encode mode,

REFL pins are connected by short jumpers in an internal

layer. To minimize the inductance of these jumpers they

can be placed in a small hole in the GND plane on the

second board layer.

相关PDF资料 |

PDF描述 |

|---|---|

| VX-53-1C23 | SWITCH LEVER SPDT 5A .187QC |

| 370 | T 1 3/4 18V .04 AMP LAMP |

| DC1620A-J | BOARD DEMO 65MSPS LTC2142-14 |

| 1850 | LAMP T3-1/4 MINI BAYONET BASE |

| 89 | LAMP INCAND G-6 S.C. BAYONET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DC1620A-L | 功能描述:BOARD DEMO 25MSPS LTC2140-14 RoHS:是 类别:未定义的类别 >> 其它 系列:* 标准包装:1 系列:* 其它名称:MS305720A |

| DC1620A-M | 功能描述:BOARD DEMO 125MSPS LTC2145-12 RoHS:是 类别:未定义的类别 >> 其它 系列:* 标准包装:1 系列:* 其它名称:MS305720A |

| DC1620A-N | 功能描述:BOARD DEMO 105MSPS LTC2144-12 RoHS:是 类别:未定义的类别 >> 其它 系列:* 标准包装:1 系列:* 其它名称:MS305720A |

| DC1620A-O | 功能描述:BOARD DEMO 80MSPS LTC2143-12 RoHS:是 类别:未定义的类别 >> 其它 系列:* 标准包装:1 系列:* 其它名称:MS305720A |

| DC1620A-P | 功能描述:BOARD DEMO 65MSPS LTC2142-12 RoHS:是 类别:未定义的类别 >> 其它 系列:* 标准包装:1 系列:* 其它名称:MS305720A |

发布紧急采购,3分钟左右您将得到回复。