- 您现在的位置:买卖IC网 > PDF目录17076 > DC245A-A (Linear Technology)BOARD EVAL LTC1668 PDF资料下载

参数资料

| 型号: | DC245A-A |

| 厂商: | Linear Technology |

| 文件页数: | 8/24页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL LTC1668 |

| 设计资源: | DC245A Design File DC245A Schematic |

| 标准包装: | 1 |

| DAC 的数量: | 1 |

| 位数: | 16 |

| 采样率(每秒): | 50M |

| 数据接口: | 并联 |

| 设置时间: | 20ns |

| DAC 型: | 电流 |

| 工作温度: | 0°C ~ 70°C |

| 已供物品: | 板 |

| 已用 IC / 零件: | LTC1668 |

| 相关产品: | LTC1668CG#PBF-ND - IC DAC 16BIT 50MSPS 28-SSOP LTC1668IG#PBF-ND - IC D/A CONV 16BIT 50MSPS 28-SSOP LTC1668CG#TRPBF-ND - IC D/A CONV 16BIT 50MSPS 28-SSOP LTC1668IG#TRPBF-ND - IC D/A CONV 16BIT 50MSPS 28-SSOP LTC1668IG-ND - IC DAC 16BIT 50MSPS 28SSOP LTC1668IG#TR-ND - IC DAC 16BIT 50MSPS 28SSOP LTC1668CG#TR-ND - IC DAC 16BIT 50MSPS 28SSOP LTC1668CG-ND - IC D/A CONV 16BIT 50MSPS 28-SSOP |

16

LTC1666/LTC1667/LTC1668

APPLICATIO S I FOR ATIO

WU

UU

cluding the output signal band of interest. Therefore, any

direct coupling of the digital signals to the analog output

will produce spurious tones that vary with the exact digital

input pattern.

Clock jitter should be minimized to avoid degrading the

noise floor of the device in AC applications, especially

where high output frequencies are being generated. Any

noise coupling from the digital inputs to the clock input will

cause phase modulation of the clock signal and the DAC

waveform, and can produce spurious tones. It is normally

best to place the digital data transitions near the falling

clock edge, well away from the active rising clock edge.

Because the clock signal contains spectral components

only at the sampling frequency and its multiples, it is

usually not a source of in band spurious tones. Overall, it

is better to treat the clock as you would an analog signal

and route it separately from the digital data input signals.

The clock trace should be routed either over the analog

ground plane or over its own section of the ground plane.

The clock line needs to have accurately controlled imped-

ance and should be well terminated near the LTC1666/

LTC1667/LTC1668.

Printed Circuit Board Layout Considerations—

Grounding, Bypassing and Output Signal Routing

The close proximity of high frequency digital data lines and

high dynamic range, wide-band analog signals makes

clean printed circuit board design and layout an absolute

necessity. Figures 11 to 15 are the printed circuit board

layers for an AC evaluation circuit for the LTC1668. Ground

planes should be split between digital and analog sections

as shown. All bypass capacitors should have minimum

trace length and be ceramic 0.1

F or larger with low ESR.

Bypass capacitors are required on VSS, VDD and REFOUT,

and all connected to the AGND plane. The COMP2 pin ties

to a node in the output current switching circuitry, and it

requires a 0.1

F bypass capacitor. It should be bypassed

to VSS along with COMP1. The AGND and DGND pins

should both tie directly to the AGND plane, and the tie point

between the AGND and DGND planes should nominally be

near the DGND pin. LADCOM should either be tied directly

to the AGND plane or be bypassed to AGND. The IOUTA and

IOUT B traces should be close together, short, and well

matched for good AC CMRR. The transformer output

ground should be capable of optionally being isolated or

being tied to the AGND plane, depending on which gives

better performance in the system.

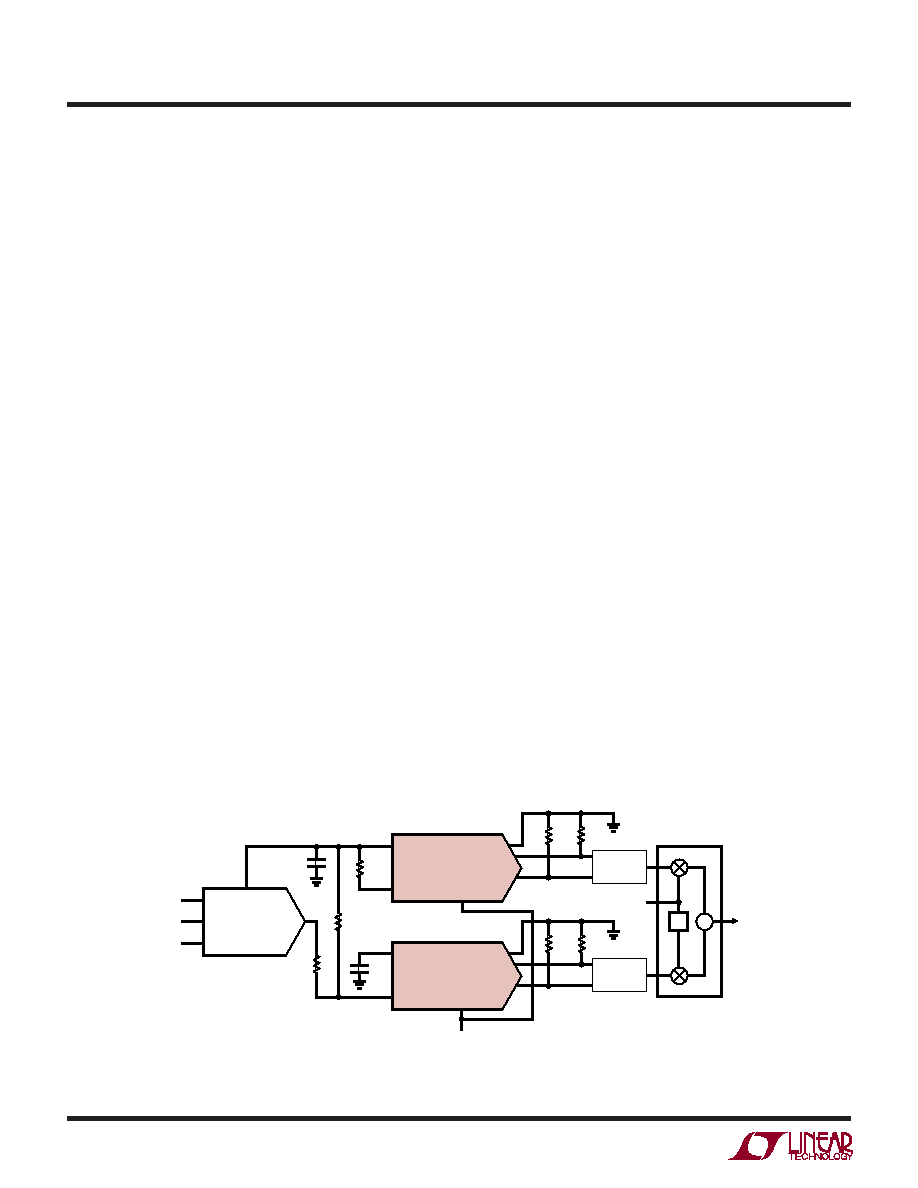

Suggested Evaluation Circuit

Figure 10 is the schematic and Figures 11 to 15 are the

circuit board layouts for a suggested evaluation circuit,

DC245A. The circuit can be programmed with component

selection and jumpers for a variety of differentially coupled

transformer output and differential and single-ended re-

sistor loaded output configurations.

REFOUT

LADCOM

IOUT A

VOUT

IOUT B

I

REFIN

CLK

LTC1668

U2

Q-CHANNEL

REFOUT

LADCOM

IOUT A

IOUT B

I

REFIN

CLK

LTC1668

U1

I-CHANNEL

52.3

52.3

52.3

52.3

LOW-PASS

FILTER

LOW-PASS

FILTER

CLOCK

INPUT

REF

1/2 LTC1661

U3

SERIAL

INPUT

2k

2.1k

21k

0.1

F

0.1

F

90

°

∑

LOCAL

OSCILLATOR

QAM

OUTPUT

QUADRATURE

MODULATOR

±5%

RELATIVE GAIN

ADJUSTMENT RANGE

1666/7/8 F10

Figure 9. QAM Modulation Using LTC1668 with

Digitally Controlled I vs Q Channel Gain Adjustment

相关PDF资料 |

PDF描述 |

|---|---|

| EVAL-AD5570SDZ | BOARD EVAL FOR AD5570 |

| FPF2006 | IC SWITCH LOAD FULL FUNC SC70-5 |

| UCS2G680MNY9 | CAP ALUM 68UF 400V 20% RADIAL |

| UPB2D391MRD | CAP ALUM 390UF 200V 20% RADIAL |

| MIC94095YMT TR | IC LOAD SW HGH SIDE 1.2A 4-TMLF |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DC-24-600-2.1 | 制造商:SR Components Inc 功能描述: |

| DC-24-600-2.1P | 制造商:SR COMPONENTS 功能描述: 制造商:SR Components Inc 功能描述: |

| DC24660 | 制造商:Cinch Connectors 功能描述:Connector Accessories Junction Shell Deep Straight Clamp 37 POS 制造商:Cinch Connectors 功能描述:CONN BACKSHELL DB37 STEEL 制造商:Cinch Connectors 功能描述:JUNCTION SHELL SIZE DC STEEL 制造商:ITT Interconnect Solutions 功能描述:METAL CONNECTOR BACKSHELL 制造商:Cinch Connectors 功能描述:JUNCTION SHELL, SIZE DC, STEEL 制造商:Cinch Connectors 功能描述:JUNCTION SHELL, SIZE DC, STEEL; Series:DC; D Sub Shell Size:DC; Connector Body Material:Steel; Cable Exit Angle:180; Accessory Type:Junction Shell Clamp; Connector Shell Size:DC; Connector Type:Straight; Enclosure Material:Steel ;RoHS Compliant: No 制造商:Cinch Connectors 功能描述:DSUB DC DEEP STRT B/S CAD 制造商:ITT Interconnect Solutions 功能描述:DEEP STRAIGHT CLAMP, SIZE DC, STEEL; Series:-; D Sub Shell Size:DC; Connector Body Material:Steel; Cable Exit Angle:180; Accessory Type:Deep Straight Clamp; Connector Shell Size:DC; Enclosure Material:Steel; External Depth:1.563" ;RoHS Compliant: No 制造商:ITT Interconnect Solutions 功能描述:Connector Accessories Backshell Carbon Steel Yellow Chromate Over Cadmium 制造商:ITT 功能描述:CONNECTOR ACCESSORIES BACKSHELL CARBON STEEL YELLOW CHROMATE OVER CADMIUM |

| DC-24660 | 功能描述:D-Sub标准连接器 37C DEEP STRT CLMP RoHS:否 制造商:Omron Electronics 位置/触点数量:9 排数:2 型式:Female 安装风格:Through Hole 安装角:Right 端接类型:Solder 过滤: |

| DC24660-11 | 制造商:ITT Interconnect Solutions 功能描述:DSUB DC DEEP STRT B/S BRASS 制造商:ITT Interconnect Solutions 功能描述:DC2466011 / 024660-0011 / D Sub |

发布紧急采购,3分钟左右您将得到回复。