- 您现在的位置:买卖IC网 > PDF目录378586 > DS1244YP-70 CAT5E PATCH CORD 30 FOOT BEIGE PDF资料下载

参数资料

| 型号: | DS1244YP-70 |

| 英文描述: | CAT5E PATCH CORD 30 FOOT BEIGE |

| 中文描述: | 256k非易失SRAM与幻影时钟 |

| 文件页数: | 13/19页 |

| 文件大小: | 292K |

| 代理商: | DS1244YP-70 |

ADS1244

SBAS273

13

www.ti.com

SLEEP MODE

Sleep Mode dramatically reduces power consumption (typi-

cally < 1

μ

W with CLK stopped) by shutting down all of the

active circuitry. To enter Sleep Mode, simply hold SCLK

HIGH after

DRDY/DOUT

goes LOW, as shown in Figure 15.

Sleep Mode can be initiated at any time during read back; it

is not necessary to retrieve all 24 bits of data beforehand.

Once t

11

has passed with SCLK held HIGH, Sleep Mode will

activate.

DRDY/DOUT

stays HIGH once Sleep Mode begins.

SCLK must remain HIGH to stay in Sleep Mode. To exit

Sleep Mode (

“

wakeup

”

), set SCLK LOW. The first data after

exiting Sleep Mode is valid. It is not necessary to stop CLK

during Sleep Mode, but doing so will further reduce the digital

supply current.

Sleep Mode With Self-Calibration

Self-calibration can be set to run immediately after exiting

Sleep Mode. This is useful when the ADS1244 is put in Sleep

Mode for long periods of time and self-calibration is desired

afterwards to compensate for temperature or supply voltage

changes.

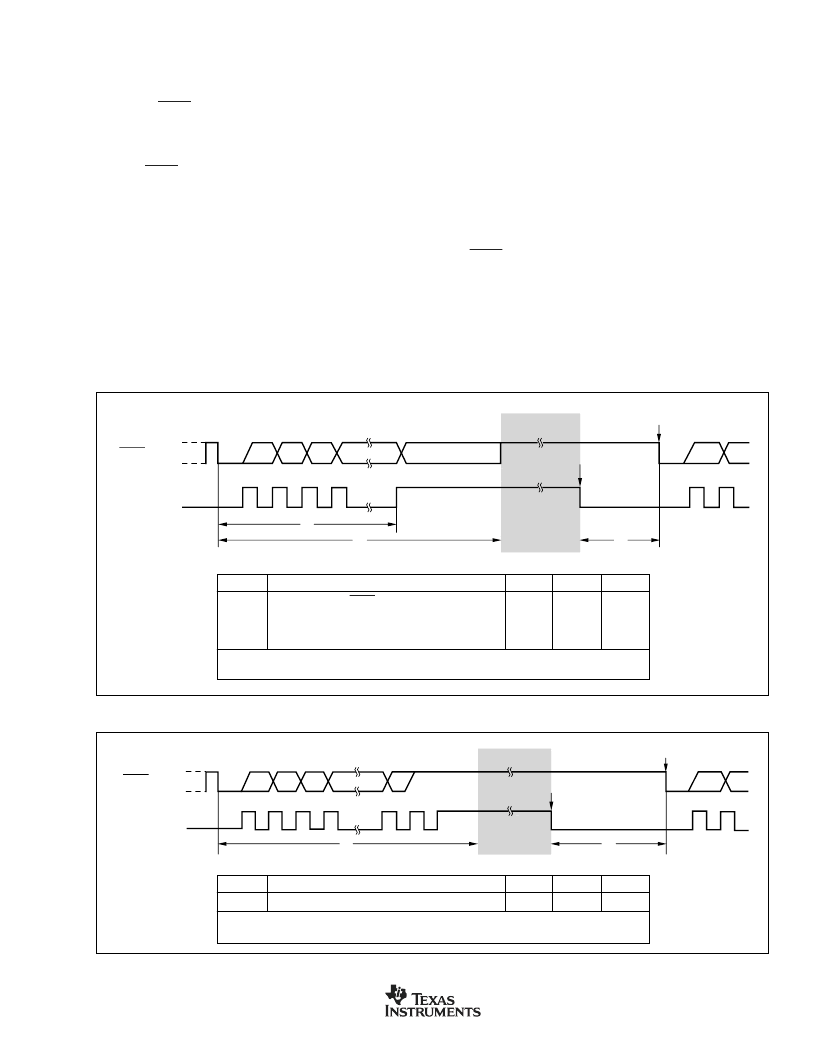

FIGURE 16. Sleep Mode with Self-Calibration on Wakeup Timing; Can be Used for Single Conversions.

SYMBOL

DESCRIPTION

MIN

MAX

UNITS

t

13(1)

Data ready after wakeup and calibration.

210

211

ms

NOTE: (1) Values given for f

CLK

= 2.4576MHz. For different CLK frequencies, scale proportional to CLK

period.

Sleep Mode

Wakeup and begin cal.

Data ready after wakeup and cal.

t

11

t

13

DRDY/DOUT

23

1

24

25

22

21

0

23

SCLK

To force a self-calibration with Sleep Mode, shift 25 bits out

before taking SCLK HIGH to enter Sleep Mode. Self-calibra-

tion will then begin after wakeup. Figure 16 shows the

appropriate timing. Note the extra time needed after wakeup

for calibration before data is ready. The first data after Sleep

Mode with self-calibration is fully-settled and can be used.

SINGLE CONVERSIONS

When only single conversions are needed, Sleep Mode can

be used to start and stop the ADS1244. To make a single

conversion, first enter the Sleep Mode holding SCLK HIGH.

Now, when ready to start the conversion, take SCLK LOW.

The ADS1244 will wake up and begin the conversion. Wait

for

DRDY/DOUT

to go LOW, and then retrieve the data.

Afterwards, take SCLK HIGH to stop the ADS1244 from

converting and re-enter Sleep Mode. Continue to hold SCLK

HIGH until ready to start the next conversion. Operating in

this fashion greatly reduces power consumption since the

ADS1244 is shut down while idle between conversions. Self-

calibrations can be performed prior to the start of the single

conversions by using the waveform shown in Figure 16.

FIGURE 15. Sleep Mode Timing; Can be Used for Single Conversions.

DRDY/DOUT

23

22

21

1

24

0

23

SCLK

Sleep Mode

Wakeup

Data ready after wakeup.

t

10

t

11

t

12

SYMBOL

DESCRIPTION

MIN

MAX

UNITS

t

10(1)

SCLK HIGH after

DRDY/DOUT

goes LOW to activate

Sleep Mode.

Sleep Mode activation Time.

Data ready after wakeup.

0

63.7

ms

t

11(1)

t

12(1)

66.5

71

66.5

72

ms

ms

NOTE: (1) Values given for f

CLK

= 2.4576MHz. For different CLK frequencies, scale proportional to CLK

period.

相关PDF资料 |

PDF描述 |

|---|---|

| DS1244Y-70 | 256k NV SRAM with Phantom Clock |

| DS1244W-120 | 256k NV SRAM with Phantom Clock |

| DS1244WP-120 | 256k NV SRAM with Phantom Clock |

| DS1244 | Low-Power, 24-Bit ANALOG-TO-DIGITAL CONVERTER |

| DS1248 | 1024k NV SRAM with Phantom Clock |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS1244YP-70+ | 功能描述:实时时钟 256k NV SRAM w/Phantom Clock RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| DS-1244ZJ | 制造商:Hikvision USA 功能描述:DOME CAM CEILING TRIM BRACKET4.75IN X .95IN 制造商:HIKVISION 功能描述:DOME CAM CEILING TRIM BRACKET 4.75IN X .95IN |

| DS1245 | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:3.3V 1024k Nonvolatile SRAM |

| DS1245AB | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:1024k Nonvolatile SRAM |

| DS1245AB-100 | 功能描述:NVRAM 1024K SRAM Nonvolatile RoHS:否 制造商:Maxim Integrated 数据总线宽度:8 bit 存储容量:1024 Kbit 组织:128 K x 8 接口类型:Parallel 访问时间:70 ns 电源电压-最大:5.5 V 电源电压-最小:4.5 V 工作电流:85 mA 最大工作温度:+ 70 C 最小工作温度:0 C 封装 / 箱体:EDIP 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。