- 您现在的位置:买卖IC网 > PDF目录19961 > DS1350WP-150IND (Maxim Integrated)IC NVSRAM 4MBIT 150NS 34PCM PDF资料下载

参数资料

| 型号: | DS1350WP-150IND |

| 厂商: | Maxim Integrated |

| 文件页数: | 8/10页 |

| 文件大小: | 0K |

| 描述: | IC NVSRAM 4MBIT 150NS 34PCM |

| 标准包装: | 1 |

| 格式 - 存储器: | RAM |

| 存储器类型: | NVSRAM(非易失 SRAM) |

| 存储容量: | 4M (512K x 8) |

| 速度: | 150ns |

| 接口: | 并联 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 34-PowerCap? 模块 |

| 供应商设备封装: | 34-PowerCap 模块 |

| 包装: | 管件 |

�� �

�

�

�DS1345W�

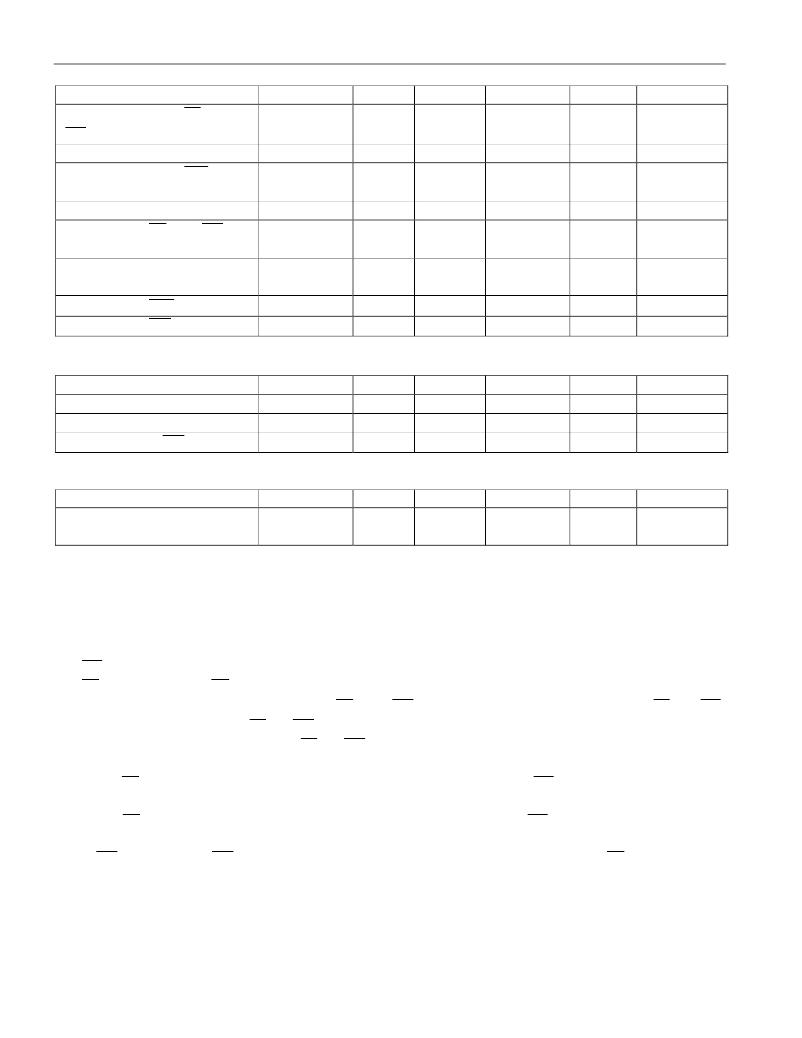

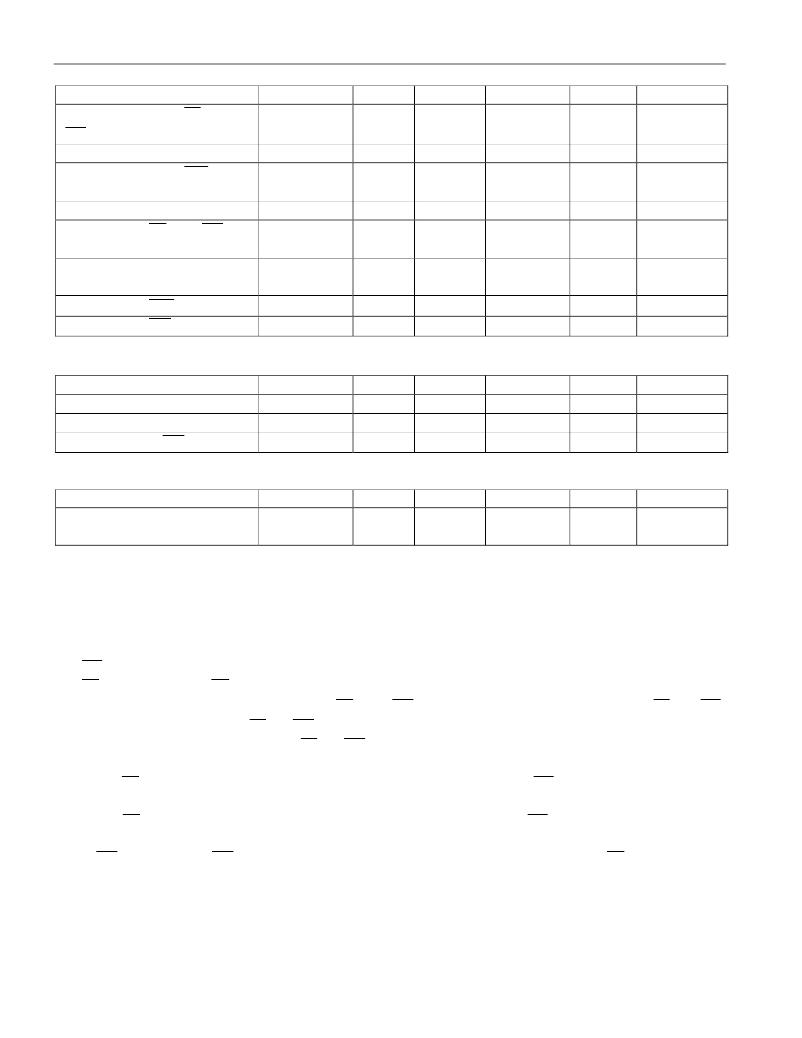

�POWER-DOWN/POWER-UP� TIMING�

�(T� A� :� See� Note� 10)�

�PARAMETER�

�V� C� C� Fail� Detect� to� CE� and�

�WE� Inactive�

�SYMBOL�

�t� PD�

�MIN�

�TYP�

�MAX�

�1.5�

�UNITS�

�μs�

�NOTES�

�11�

�V� CC� slew� from� V� TP� to� 0V�

�t� F�

�150�

�μs�

�V� CC� Fail� Detect� to� RST�

�Active�

�V� CC� slew� from� 0V� to� V� TP�

�V� CC� Valid� to� CE� and� WE�

�Inactive�

�V� CC� Valid� to� End� of� Write�

�Protection�

�t� RPD�

�t� R�

�t� PU�

�t� REC�

�150�

�15�

�2�

�125�

�μs�

�μs�

�ms�

�ms�

�14�

�V� CC� Valid� to� RST� Inactive�

�V� CC� Valid� to� BW� Valid�

�t� RPU�

�t� BPU�

�150�

�200�

�350�

�1�

�ms�

�s�

�14�

�14�

�BATTERY� WARNING� TIMING�

�(T� A� :� See� Note� 10)�

�PARAMETER�

�SYMBOL�

�MIN�

�TYP�

�MAX�

�UNITS�

�NOTES�

�Battery� Test� Cycle�

�Battery� Test� Pulse� Width�

�Battery� Test� to� BW� Active�

�t� BTC�

�t� BTPW�

�t� BW�

�24�

�1�

�1�

�hr�

�s�

�s�

�(T� A� =� +25°C)�

�PARAMETER�

�Expected� Data�

�Retention� Time�

�SYMBOL�

�t� DR�

�MIN�

�10�

�TYP�

�MAX�

�UNITS�

�years�

�NOTES�

�9�

�WARNING:�

�Under� no� circumstance� are� negative� undershoots,� of� any� amplitude,� allowed� when� device� is� in� battery�

�backup� mode.�

�NOTES:�

�1.� W� E� is� high� for� a� read� cycle.�

�2.� OE� =� V� IH� or� V� IL� .� If� OE� =� V� IH� during� write� cycle,� the� output� buffers� remain� in� a� high� impedance� state.�

�3.� t� WP� is� specified� as� the� logical� AND� of� CE� and� WE� .� t� WP� is� measured� from� the� latter� of� CE� or� WE�

�going� low� to� the� earlier� of� CE� or� WE� going� high.�

�4.� t� DS� is� measured� from� the� earlier� of� CE� or� WE� going� high.�

�5.� These� parameters� are� sampled� with� a� 5� pF� load� and� are� not� 100%� tested.�

�6.� If� the� CE� low� transition� occurs� simultaneously� with� or� latter� than� the� WE� low� transition,� the� output�

�buffers� remain� in� a� high� impedance� state� during� this� period.�

�7.� If� the� CE� high� transition� occurs� prior� to� or� simultaneously� with� the� WE� high� transition,� the� output�

�buffers� remain� in� high� impedance� state� during� this� period.�

�8.� If� WE� is� low� or� the� WE� low� transition� occurs� prior� to� or� simultaneously� with� the� CE� low� transition,�

�the� output� buffers� remain� in� a� high� impedance� state� during� this� period.�

�9.� Each� DS1345W� has� a� built-in� switch� that� disconnects� the� lithium� source� until� V� CC� is� first� applied� by�

�the� user.� The� expected� t� DR� is� defined� as� accumulative� time� in� the� absence� of� V� CC� starting� from� the�

�time� power� is� first� applied� by� the� user.�

�8� of� 10�

�相关PDF资料 |

PDF描述 |

|---|---|

| T95R227M6R3HSAL | CAP TANT 220UF 6.3V 20% 2824 |

| R12P212S | CONV DC/DC 2W 12V OUT SIP VERT |

| DS1350ABP-70IND | IC NVSRAM 4MBIT 70NS 34PCM |

| DS1350ABP-70 | IC NVSRAM 4MBIT 70NS 34PCM |

| LTC4210-2IS6#TRMPBF | IC CONTROLLER HOT SWAP TSOT23-6 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS1350WP-150-IND | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:3.3V 4096K Nonvolatile SRAM with Battery Monitor |

| DS1350Y | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:4096k Nonvolatile SRAM with Battery Monitor |

| DS1350Y/AB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:4096k Nonvolatile SRAM with Battery Monitor |

| DS1350Y-70 | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:4096k Nonvolatile SRAM with Battery Monitor |

| DS1350YL-100 | 功能描述:IC NVSRAM 4MBIT 100NS 34LPM RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:150 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:4K (2 x 256 x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:2.5 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-VFDFN 裸露焊盘 供应商设备封装:8-DFN(2x3) 包装:管件 产品目录页面:1445 (CN2011-ZH PDF) |

发布紧急采购,3分钟左右您将得到回复。