- 您现在的位置:买卖IC网 > PDF目录21989 > DS1621V/T&R (Maxim Integrated)IC THERMOMETER/STAT DIG 8-SOIC PDF资料下载

参数资料

| 型号: | DS1621V/T&R |

| 厂商: | Maxim Integrated |

| 文件页数: | 7/16页 |

| 文件大小: | 337K |

| 描述: | IC THERMOMETER/STAT DIG 8-SOIC |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,000 |

| 功能: | 温度计,恒温计 |

| 传感器类型: | 内部 |

| 感应温度: | -55°C ~ 125°C |

| 精确度: | ±2°C(最小值) |

| 拓扑: | ADC(三角积分型),比较器,寄存器库 |

| 输出类型: | I²C?/SMBus? |

| 输出警报: | 是 |

| 输出风扇: | 无 |

| 电源电压: | 2.7 V ~ 5.5 V |

| 工作温度: | -55°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-SOIC(0.209",5.30mm 宽) |

| 供应商设备封装: | 8-SOIC |

| 包装: | 带卷 (TR) |

DS1621

7 of 16

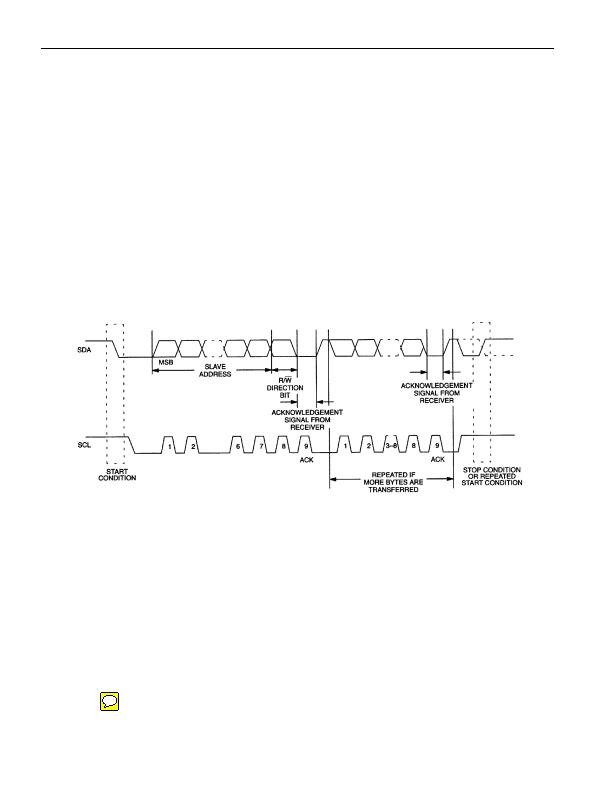

Each data transfer is initiated with a START condition and terminated with a STOP condition. The

number of data bytes transferred between START and STOP conditions is not limited and is determined

by the master device. The information is transferred byte-wise and each receiver acknowledges with a

ninth-bit.

Within the bus specifications a regular mode (100kHz clock rate) and a fast mode (400kHz clock rate) are

defined. The DS1621 works in both modes.

Acknowledge: Each receiving device, when addressed, is obliged to generate an acknowledge after the

reception of each byte. The master device must generate an extra clock pulse which is associated with this

acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a

way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of

course, setup and hold times must be taken into account. A master must signal an end of data to the slave

by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case,

the slave must leave the data line HIGH to enable the master to generate the STOP condition.

Figure 4. DATA TRANSFER ON 2-WIRE SERIAL BUS

Figure 4 details how data transfer is accomplished on the 2-wire bus. Depending upon the state of the

R/W bit, two types of data transfer are possible:

1. Data transfer from a master transmitter to a slave receiver. The first byte transmitted by the

master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge

bit after each received byte.

2. Data transfer from a slave transmitter to a master receiver. The first byte, the slave address, is

transmitted by the master. The slave then returns an acknowledge bit. Next follows a number of data

bytes transmitted by the slave to the master. The master returns an acknowledge bit after all received

bytes other than the last byte. At the end of the last received byte, a not acknowledge is returned.

The master device generates all of the serial clock pulses and the START and STOP conditions. A

transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START

condition is also the beginning of the next serial transfer, the bus will not be released.

相关PDF资料 |

PDF描述 |

|---|---|

| EP2S30F484C5 | IC STRATIX II FPGA 30K 484-FBGA |

| FMC10DREH-S13 | CONN EDGECARD 20POS .100 EXTEND |

| XC3S200-4PQG208C | IC SPARTAN-3 FPGA 200K 208-PQFP |

| TACR476M004RTA | CAP TANT 47UF 4V 20% 0805 |

| ABC49DRTN-S13 | CONN EDGECARD 98POS .100 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS-1621ZJ | 制造商:Hikvision USA 功能描述:6" Outdoor Speed Dome Bracket, White, Pole Mount 制造商:HIKVISION 功能描述:MOUNT |

| DS1622 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Industrial Control IC |

| DS1622S | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Industrial Control IC |

| DS-1622ZJ | 制造商:Hikvision USA 功能描述:Pendant Pole Mount Bracket 4.6In X 7.65In X 12.2In |

| DS1623 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:IC-DIGITAL THERMOSTAT |

发布紧急采购,3分钟左右您将得到回复。