- 您现在的位置:买卖IC网 > PDF目录97862 > DS1685S-3 (MAXIM INTEGRATED PRODUCTS INC) 1 TIMER(S), REAL TIME CLOCK, PDSO24 PDF资料下载

参数资料

| 型号: | DS1685S-3 |

| 厂商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分类: | Timer or RTC |

| 英文描述: | 1 TIMER(S), REAL TIME CLOCK, PDSO24 |

| 封装: | 0.300 INCH, SOP-24 |

| 文件页数: | 16/34页 |

| 文件大小: | 455K |

| 代理商: | DS1685S-3 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

DS1685/DS1687 3V/5V Real-Time Clocks

23 of 34

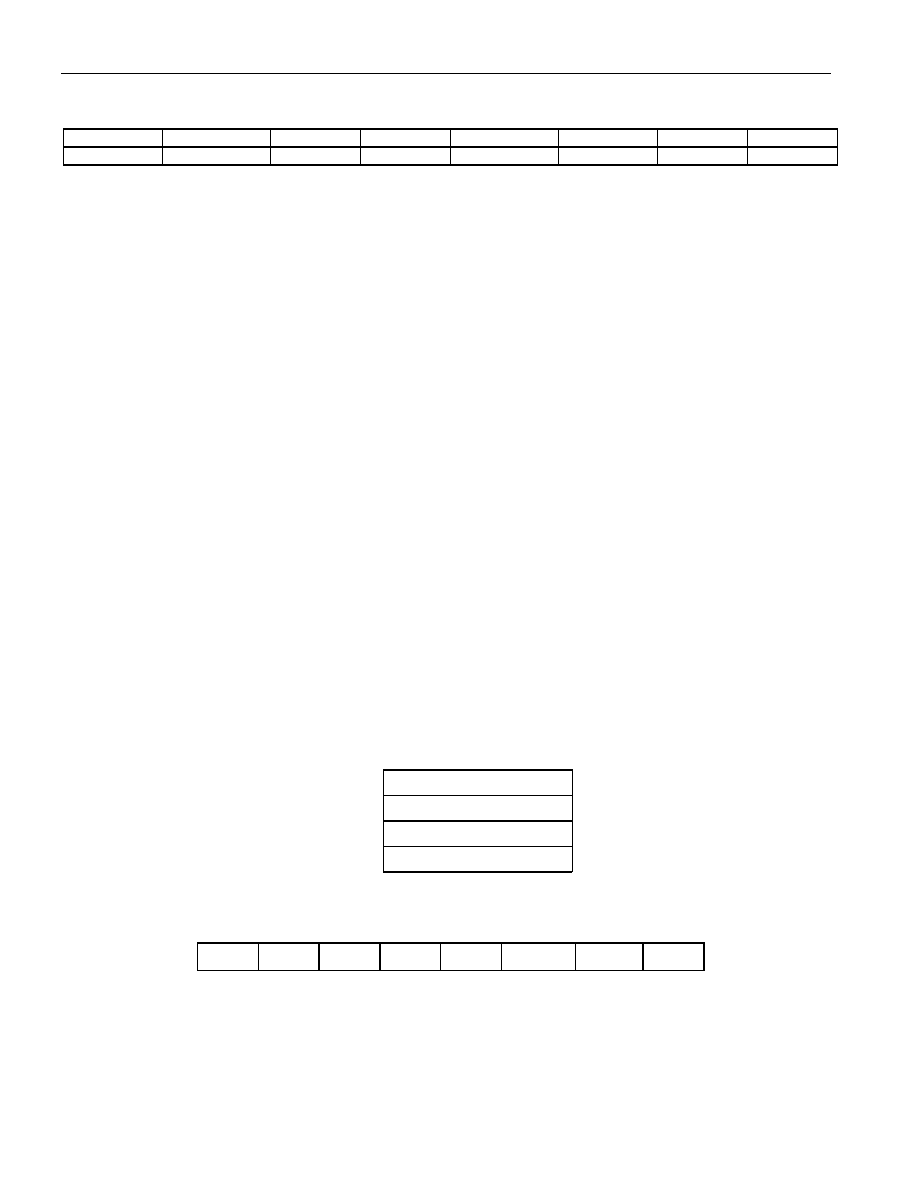

Extended Control Register 4B

MSB

LSB

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

ABE

E32K

CS

RCE

PRS

RIE

WIE

KSE

ABE – Auxiliary Battery Enable. This bit when written to a logic 1 enables the VBAUX pin for extended functions.

E32K – Enable 32.768kHz output. This bit when written to a logic 1 enables the 32.768kHz oscillator frequency to

be output on the SQW pin. This bit is set to a logic 1 when VCC is applied.

CS – Crystal Select Bit. When CS is set to a 0, the oscillator is configured for operation with a crystal that has a

6pF specified load capacitance. When CS = 1, the oscillator is configured for a 12.5pF crystal. CS is disabled in the

DS1687 EDIP and should be set to CS = 0.

RCE – RAM Clear-Enable bit. When set to a 1, this bit enables a low level on

RCLR to clear all 242 bytes of user

RAM. When RCE = 0,

RCLR and the RAM clear function are disabled.

PRS – PAB Reset-Select Bit. When set to a 0, the

PWR pin is set high-Z when the DS1685 goes into power-fail.

When set to a 1, the PWR pin remains active upon entering power-fail.

RIE – Ram Clear-Interrupt Enable. When RIE is set to a 1, the

IRQ pin is driven low when a RAM clear function is

completed.

WIE – Wake-Up Alarm-Interrupt Enable. When VCC voltage is absent and WIE is set to a 1, the PWR pin is driven

active-low when a wake-up condition occurs, causing the WF bit to be set to 1. When VCC is then applied, the IRQ

pin is also driven low. If WIE is set while system power is applied, both

IRQ and PWR are driven low in response to

WF being set to 1. When WIE is cleared to a 0, the WF bit has no affect on the

PWR or IRQ pins.

KSE – Kickstart Interrupt Enable. When VCC voltage is absent and KSE is set to a 1, the PWR pin is driven active-

low when a kickstart condition occurs (

KS pulsed low), causing the KF bit to be set to 1. When V

CC is then applied,

the

IRQ pin is also driven low. If KSE is set to 1 while system power is applied, both IRQ and PWR are driven low in

response to KF being set to 1. When KSE is cleared to a 0, the KF bit has no affect on the

PWR or IRQ pins.

SYSTEM MAINTENANCE INTERRUPT (SMI) RECOVERY STACK

An SMI recovery register stack is located in the extended register bank, locations 4Eh and 4Fh. This register stack,

shown below, can be used by the BIOS to recover from an SMI occurring during an RTC read or write.

RTC ADDRESS

RTC ADDRESS-1

4Eh

RTC ADDRESS-2

4Fh

RTC ADDRESS-3

SMI RECOVERY STACK

7

6

5

4

3

2

1

0

DV0

AD6

AD5

AD4

AD3

AD2

AD1

AD0

REGISTER BIT DEFINITION

相关PDF资料 |

PDF描述 |

|---|---|

| DS1685E-5 | 1 TIMER(S), REAL TIME CLOCK, PDSO24 |

| DS1685QN-3 | 1 TIMER(S), REAL TIME CLOCK, PQCC28 |

| DS1685QN-5 | 1 TIMER(S), REAL TIME CLOCK, PQCC28 |

| DS1685SN-5 | 1 TIMER(S), REAL TIME CLOCK, PDSO24 |

| DS1687-3 | 1 TIMER(S), REAL TIME CLOCK, DIP24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS1685S-3/T&R | 功能描述:实时时钟 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| DS1685S-3/TR | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:3V/5V Real-Time Clocks |

| DS1685S-3_12 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:3V/5V Real-Time Clocks |

| DS1685S-3+ | 功能描述:实时时钟 3V/5V RTC RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| DS1685S-3+T& | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:3V/5V Real-Time Clocks |

发布紧急采购,3分钟左右您将得到回复。