- 您现在的位置:买卖IC网 > PDF目录295504 > DS1744WP-120IND+ (MAXIM INTEGRATED PRODUCTS INC) Y2K-Compliant, Nonvolatile Timekeeping RAMs PDF资料下载

参数资料

| 型号: | DS1744WP-120IND+ |

| 厂商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分类: | XO, clock |

| 英文描述: | Y2K-Compliant, Nonvolatile Timekeeping RAMs |

| 中文描述: | 0 TIMER(S), REAL TIME CLOCK, DMA34 |

| 封装: | ROHS COMPLIANT, MODULE-34 |

| 文件页数: | 11/16页 |

| 文件大小: | 176K |

| 代理商: | DS1744WP-120IND+ |

DS1744/DS1744P Y2K-Compliant, Nonvolatile Timekeeping RAMs

4 of 16

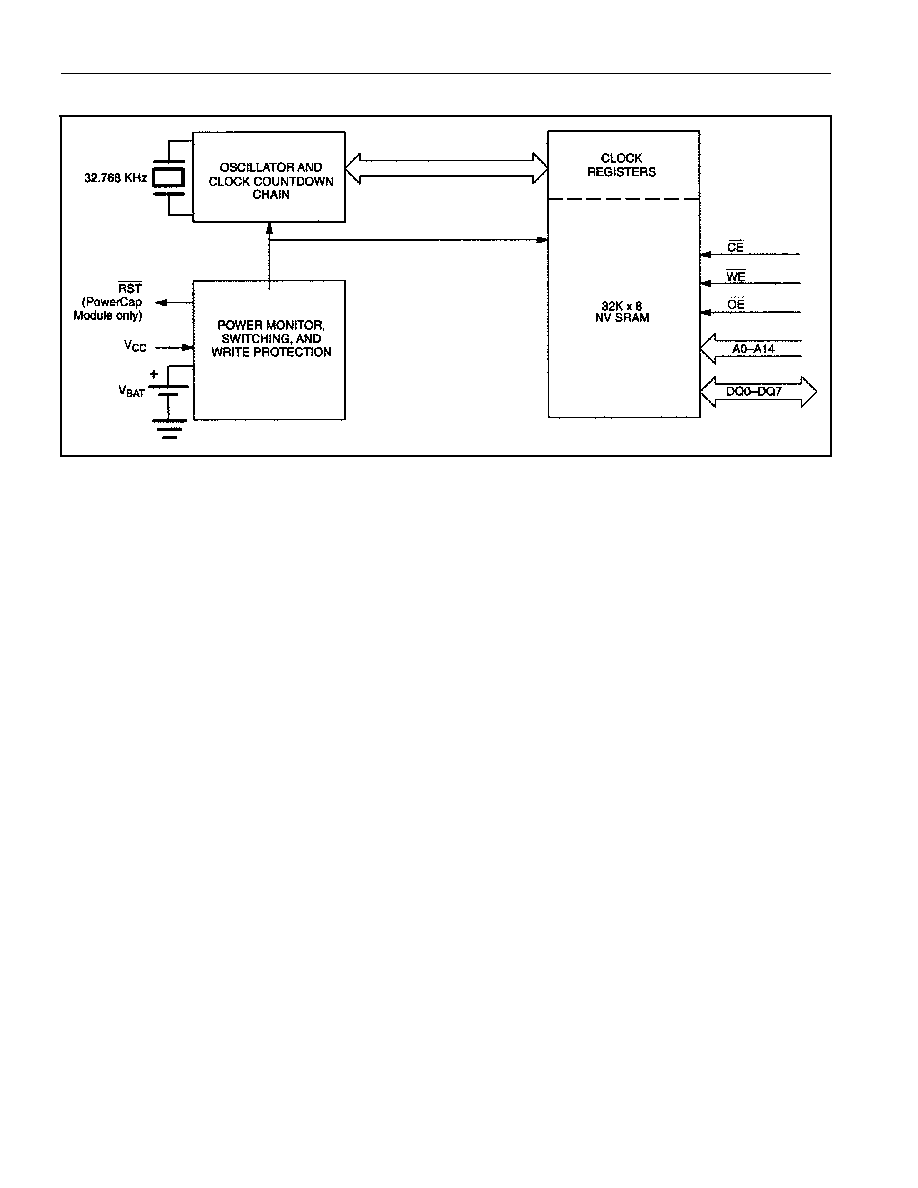

Figure 1. DS1744/DS1744P Block Diagram

PACKAGES

The DS1744 is available in two packages (28-pin encapsulated DIP and 34-pin PowerCap module). The

28-pin EDIP module integrates the crystal, lithium energy source, and silicon all in one package. The 34-

pin PowerCap module board is designed with contacts for connection to a separate PowerCap

(DS9034PCX) that contains the crystal and battery. This design allows the PowerCap to be mounted on

top of the DS1744P after the completion of the surface-mount process. Mounting the PowerCap after the

surface-mount process prevents damage to the crystal and battery due to the high temperatures required

for solder reflow. The PowerCap is keyed to prevent reverse insertion. The PowerCap module board and

PowerCap are ordered separately and shipped in separate containers. The part number for the PowerCap is

DS9034PCX.

CLOCK OPERATIONS—READING THE CLOCK

While the double-buffered register structure reduces the chance of reading incorrect data, internal updates

to the DS1744 clock registers should be halted before clock data is read to prevent reading of data in

transition. However, halting the internal clock register updating process does not affect clock accuracy.

Updating is halted when a 1 is written into the read bit, bit 6 of the century register (Table 2). As long as a

1 remains in that position, updating is halted. After a halt is issued, the registers reflect the count, that is,

day, date, and time that was current at the moment the halt command was issued. However, the internal

clock registers of the double-buffered system continue to update so that the clock accuracy is not affected

by the access of data. All the DS1744 registers are updated simultaneously after the internal clock-register

updating process has been re-enabled. Updating is within a second after the read bit is written to 0. The

READ bit must be a 0 for a minimal of 500

s to ensure the external registers are updated.

DS1744/DS1744P

相关PDF资料 |

PDF描述 |

|---|---|

| DS1746-70+ | Y2K-Compliant, Nonvolatile Timekeeping RAMs |

| DS1746-70IND+ | Y2K-Compliant, Nonvolatile Timekeeping RAMs |

| DS1746P-70+ | Y2K-Compliant, Nonvolatile Timekeeping RAMs |

| DS1746P-70IND+ | Y2K-Compliant, Nonvolatile Timekeeping RAMs |

| DS1746W-120+ | Y2K-Compliant, Nonvolatile Timekeeping RAMs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS1744WP-120IND+ | 功能描述:实时时钟 Timekeeping NV RAM RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| DS1745Y-150 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:NVRAM (Battery Based) |

| DS1745Y-150-IND | 制造商:未知厂家 制造商全称:未知厂家 功能描述:NVRAM (Battery Based) |

| DS1745Y-200 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:NVRAM (Battery Based) |

| DS1745Y-200-IND | 制造商:未知厂家 制造商全称:未知厂家 功能描述:NVRAM (Battery Based) |

发布紧急采购,3分钟左右您将得到回复。