- 您现在的位置:买卖IC网 > PDF目录9354 > DS17487-5IND+ (Maxim Integrated Products)IC RTC 5V 4K NV RAM 24-EDIP PDF资料下载

参数资料

| 型号: | DS17487-5IND+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 30/31页 |

| 文件大小: | 0K |

| 描述: | IC RTC 5V 4K NV RAM 24-EDIP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 14 |

| 类型: | 时钟/日历 |

| 特点: | 警报器,夏令时,闰年,NVSRAM,方波输出 |

| 存储容量: | 4KB |

| 时间格式: | HH:MM:SS(12/24 小时) |

| 数据格式: | YY-MM-DD-dd |

| 接口: | 并联 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 电压 - 电源,电池: | 2.5 V ~ 3.7 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 通孔 |

| 封装/外壳: | 24-DIP 模块(0.600",15.24mm) |

| 供应商设备封装: | 24-EDIP |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页

DS17285/DS17287/DS17485/DS17487/DS17885/DS17887

Real-Time Clocks

8

_____________________________________________________________________

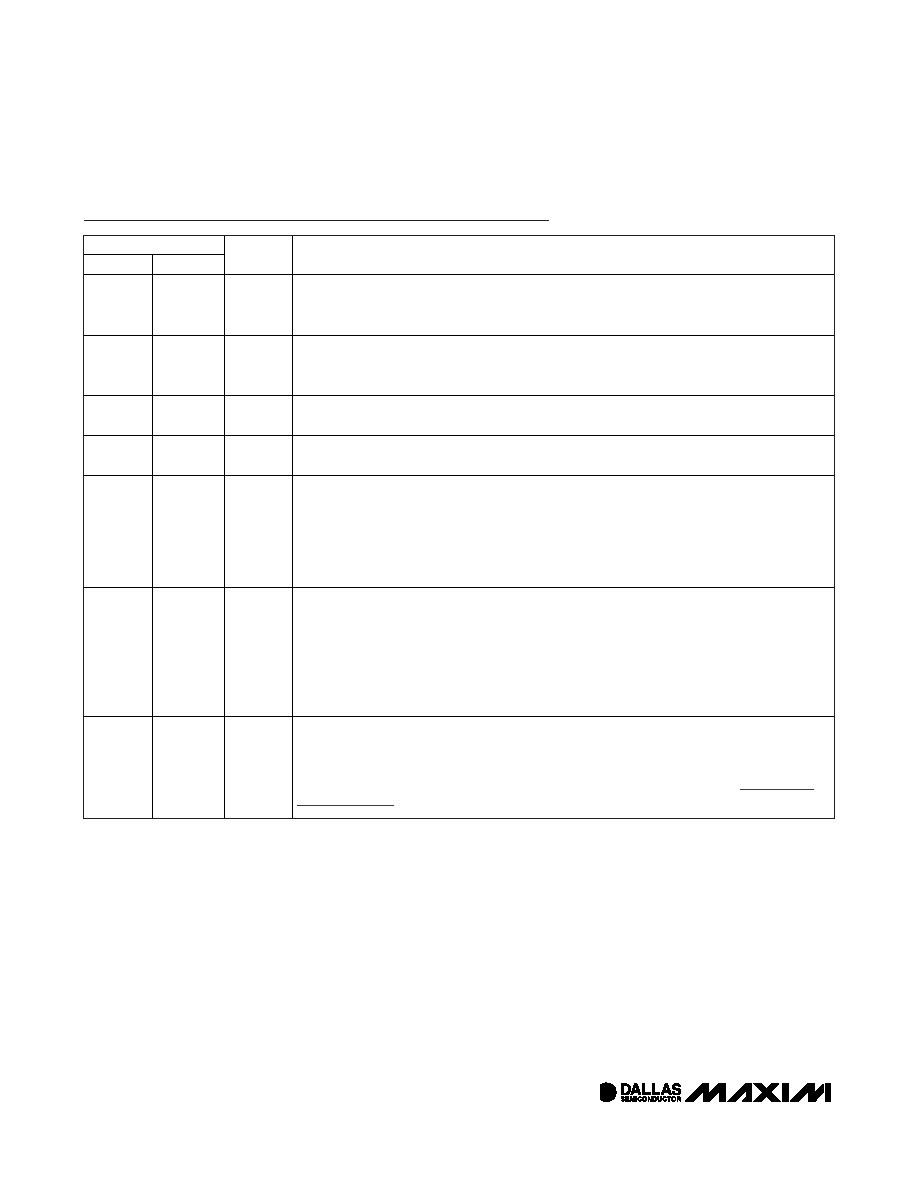

Pin Description (continued)

PIN

24

28

NAME

FUNCTION

13

23

CS

Active-Low Chip-Select Input. This pin must be asserted low during a bus cycle for the

device to be accessed.

CS must be kept in the active state during RD and WR. Bus cycles

that take place without asserting

CS latch addresses, but no access occurs.

14

24

ALE

Address Latch Enable Input, Active High. This input pin is used to demultiplex the

address/data bus. The falling edge of ALE causes the address to be latched within the

device.

15

25

WR

Active-Low Write Input. This pin defines the period during which data is written to the

addressed register.

17

27

RD

Active-Low Read Input. This pin identifies the period when the device drives the bus with

read data. It is an enable signal for the output buffers of the device.

18

28

KS

Active-Low Kickstart Input. When VCC is removed from the device, the system can be

powered on in response to an active-low transition on the

KS pin, as might be generated

from a key closure. VBAUX must be present and auxiliary-battery-enable bit (ABE) must be

set to 1 if the kickstart function is used, and the

KS pin must be pulled up to the VBAUX

supply. While VCC is applied, the

KS pin can be used as an interrupt input. If not used, KS

must be grounded and ABE set to 0.

19

1

IRQ

Active-Low Interrupt Request. This pin is an active-low output that can be used as an

interrupt input to a processor. The

IRQ output remains low as long as the status bit causing

the interrupt is present and the corresponding interrupt-enable bit is set. To clear the

IRQ

pin, the application software must clear all enabled flag bits contributing to the pin’s active

state. When no interrupt conditions are present, the

IRQ level is in the high-impedance

state. Multiple interrupting devices can be connected to an

IRQ bus, provided that they are

all open drain. The

IRQ pin requires an external pullup resistor to VCC.

20

2

VBAT

Connection for Primary Battery. This supply input is used to power the normal clock

functions when VCC is absent. Diodes placed in series between VBAT and the battery can

prevent proper operation. If VBAT is not required, the pin must be grounded. UL recognized

to ensure against reverse charging current when used with a lithium battery (www.maxim-

ic.com/qa/info/ul). This pin is missing (N.C.) on the EDIP package.

相关PDF资料 |

PDF描述 |

|---|---|

| DS17487-3IND+ | IC RTC 3V 4K NV RAM 24-EDIP |

| DS1554W-120+ | IC RTC RAM Y2K 3.3V 120NS 32EDIP |

| MCP4132T-103E/MF | IC RHEO DGTL SNGL 10K SPI 8DFN |

| DS1244WP-120IND+ | IC NVSRAM 256KBIT 120NS 34PCM |

| VE-25F-MX-B1 | CONVERTER MOD DC/DC 72V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS17487-5IND+ | 功能描述:实时时钟 3V/5V RTC RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| DS17487B-3 | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:3V/5V Real-Time Clock |

| DS17487B-5 | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:3V/5V Real-Time Clock |

| DS17487BN-3 | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:3V/5V Real-Time Clock |

| DS17487BN-5 | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:3V/5V Real-Time Clock |

发布紧急采购,3分钟左右您将得到回复。