- 您现在的位置:买卖IC网 > PDF目录9174 > DS1848E-010+T&R (Maxim Integrated Products)IC RES/MEM TEMP 10/10K 14-TSSOP PDF资料下载

参数资料

| 型号: | DS1848E-010+T&R |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 8/17页 |

| 文件大小: | 0K |

| 描述: | IC RES/MEM TEMP 10/10K 14-TSSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1,000 |

| 接片: | 256 |

| 电阻(欧姆): | 10k |

| 电路数: | 2 |

| 温度系数: | 标准值 850 ppm/°C |

| 存储器类型: | 非易失 |

| 接口: | I²C(设备位址) |

| 电源电压: | 3 V ~ 5.5 V |

| 工作温度: | -40°C ~ 95°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 14-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 14-TSSOP |

| 包装: | 带卷 (TR) |

DS1848

16 of 17

NOTES:

1) All voltages are referenced to ground.

2) Inputs SDA = SCL = WP = Vcc. A0, A1, and A2 must be tied to VCC or GND.

3) Valid at 25°C only.

4) Absolute linearity is the difference of measured value from expected value at DAC position.

Expected value is a straight line from measured minimum position to measured maximum position.

5) Relative linearity the deviation of an LSB DAC setting change vs. the expected LSB change.

Expected LSB change is the slope of the straight line from measured minimum position to measured

maximum position.

6) A fast mode device can be used in a standard mode system, but the requirement tSU:DAT > 250ns must

then be met. This will automatically be the case if the device does not stretch the LOW period of the

SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next

data bit to the SDA line tRMAX + tSU:DAT = 1000ns + 250ns = 1250ns before the SCL line is released.

7) After this period, the first clock pulse is generated.

8) The maximum t

HD:DAT has only to be met if the device does not stretch the LOW period (tLOW) of the

SCL signal.

9) A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the

VI

H MIN of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.

10) C

B — total capacitance of one bus line in picofarads, timing referenced to 0.9VCC and 0.1VCC.

11) EEPROM write begins after a stop condition occurs.

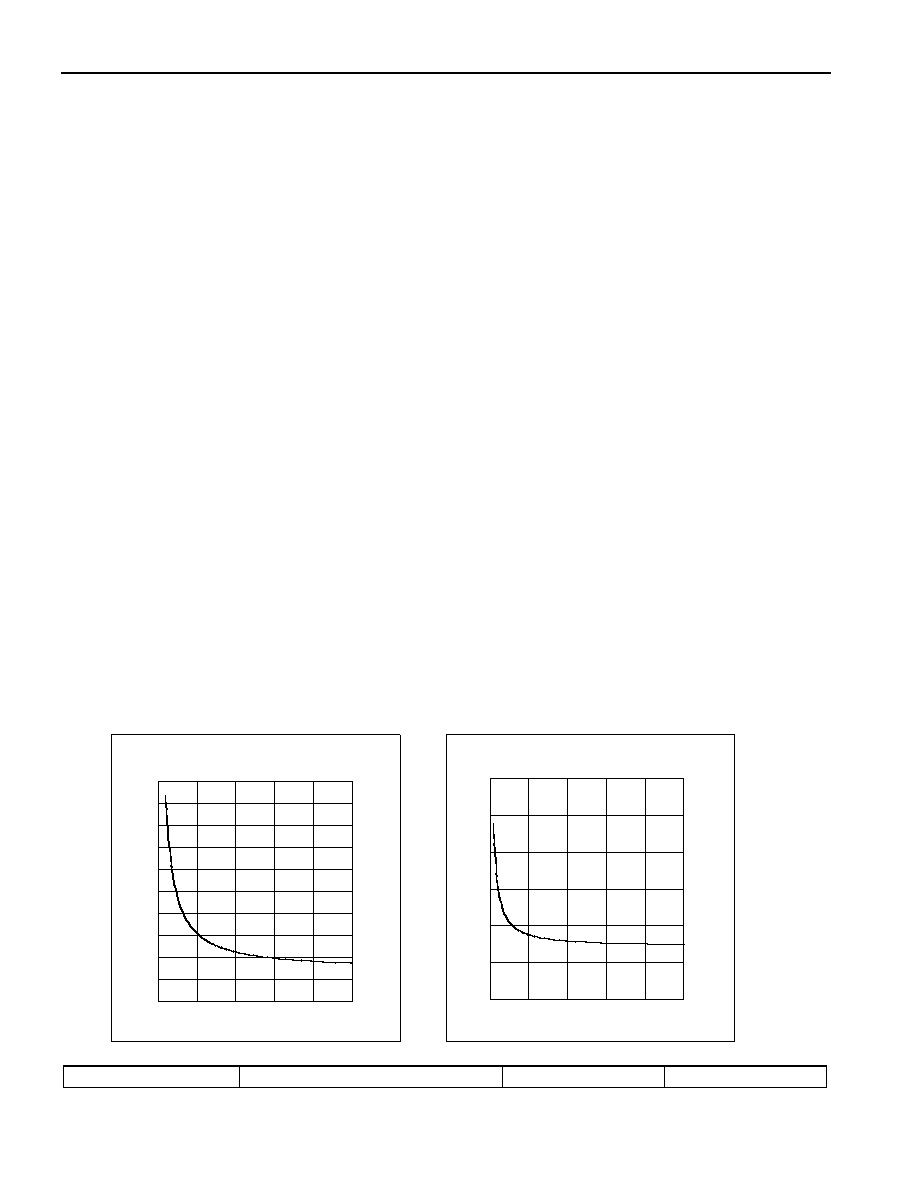

12) The temperature coefficient varies with resistor position from 650ppm/°C at position FFh to

1000ppm/°C at 00h (for the 50k resistor), or 1500ppm/°C at 00h (for the 10k resistor). See the graphs

below. The tempco can be significantly reduced by using the resistor calibration values. When doing

so, the average tempco over the entire temperature range is between 200ppm/°C (for the lower

positions) and 10ppm/°C (higher positions). Refer to the Programming the Look-Up Table section of

the data sheet.

13) I/O pins of fast mode devices must not obstruct the SDA and SCL lines if VCC is switched off.

14) Refer to Programming the Look-Up Table section of the data sheet for calibration.

15) Address input A1 passes Latch-up per JEDEC 78 class I. All other pins pass class II.

ORDERING INFORMATION

ORDERING

PACKAGE

OPERATING

VERSION

TEMPCO vs. RESISTANCE

10K RESISTOR

500

600

700

800

900

1000

1100

1200

1300

1400

1500

0

2000

4000

6000

8000

10000

RESISTANCE (OHMS)

PPM/

°C

TEMPCO vs. RESISTANCE

50K RESISTOR

500

600

700

800

900

1000

1100

0

10000

20000

30000

40000

50000

RESISTANCE (OHMS)

PPM/

°C

相关PDF资料 |

PDF描述 |

|---|---|

| DS1844E-010+T&R | IC POT DIG QUAD 10K 20-TSSOP |

| DS1844E-050+T&R | IC POT DIG QUAD 50K 20-TSSOP |

| DS1844E-100+T&R | IC POT DIG QUAD 100K 20-TSSOP |

| MAX5482ETE+ | IC POT DGTL 10BIT NV 16-TQFN |

| MAX5483ETE+ | IC POT DGTL 10BIT NV 16-TQFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS1848E-050 | 功能描述:数字电位计 IC RoHS:否 制造商:Maxim Integrated 电阻:200 Ohms 温度系数:35 PPM / C 容差:25 % POT 数量:Dual 每 POT 分接头:256 弧刷存储器:Volatile 缓冲刷: 数字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作电源电压:1.7 V to 5.5 V 电源电流:27 uA 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:TQFN-16 封装:Reel |

| DS1848E-050/S+ | 制造商:Maxim Integrated Products 功能描述:- Rail/Tube |

| DS1848E-050/T&R | 制造商:Maxim Integrated Products 功能描述:DUAL NV TEMP RES AND MEM 10/50K T&R - Tape and Reel |

| DS1848E-050/T&R | 功能描述:数字电位计 IC RoHS:否 制造商:Maxim Integrated 电阻:200 Ohms 温度系数:35 PPM / C 容差:25 % POT 数量:Dual 每 POT 分接头:256 弧刷存储器:Volatile 缓冲刷: 数字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作电源电压:1.7 V to 5.5 V 电源电流:27 uA 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:TQFN-16 封装:Reel |

| DS1848E-050/TR | 制造商:Maxim Integrated Products 功能描述:Digital Potentiometer, 14 Pin, Plastic, TSSOP |

发布紧急采购,3分钟左右您将得到回复。