- 您现在的位置:买卖IC网 > Datasheet目录222 > DS1990R-F5# (Maxim Integrated)IBUTTON SERIAL NUMBER F5 Datasheet资料下载

参数资料

| 型号: | DS1990R-F5# |

| 厂商: | Maxim Integrated |

| 文件页数: | 4/10页 |

| 文件大小: | 0K |

| 描述: | IBUTTON SERIAL NUMBER F5 |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| RoHS指令信息: | IButton RoHS Compliance Plan |

| 标准包装: | 73 |

| 系列: | iButton® |

| 存储容量: | 8B |

| 存储器类型: | ROM |

| 产品目录页面: | 1431 (CN2011-ZH PDF) |

�� �

�

�

�Serial� Number� iButton�

�64-Bit� Lasered� ROM�

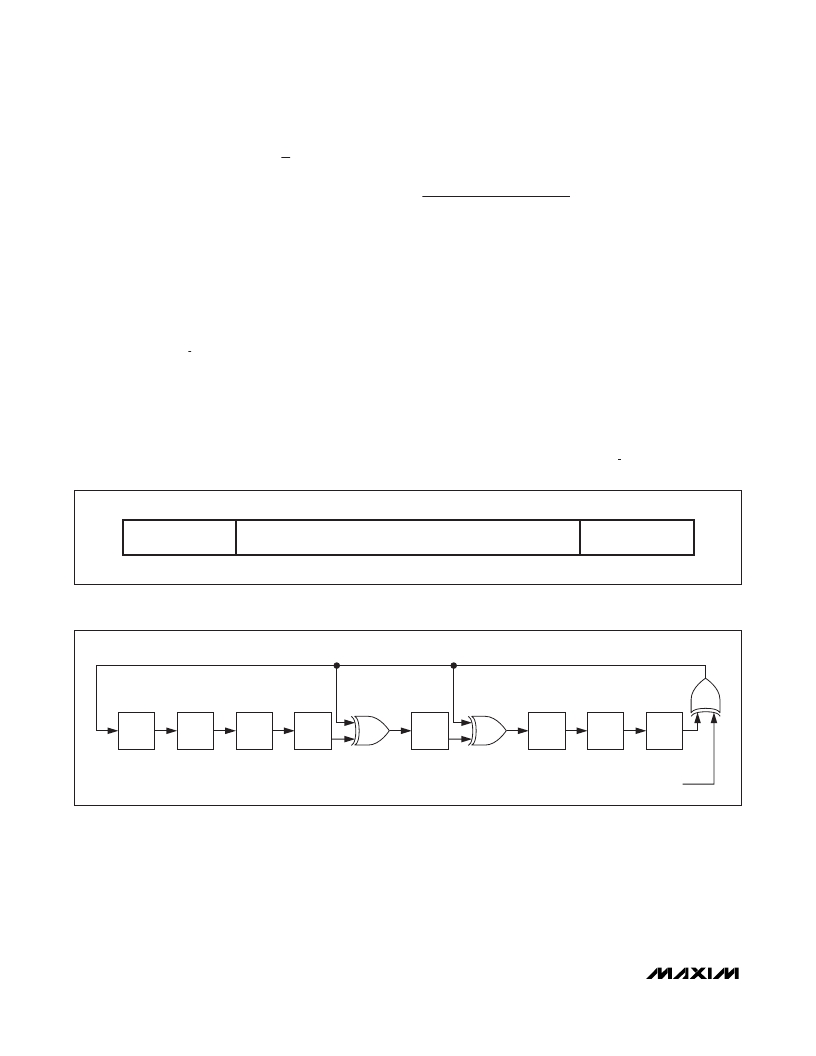

�Each� DS1990R� contains� a� unique� ROM� code� that� is� 64�

�bits� long.� The� first� 8� bits� are� a� 1-Wire� family� code.� The�

�next� 48� bits� are� a� unique� serial� number.� The� last� 8� bits�

�are� a� CRC� of� the� first� 56� bits.� See� Figure� 2� for� details.�

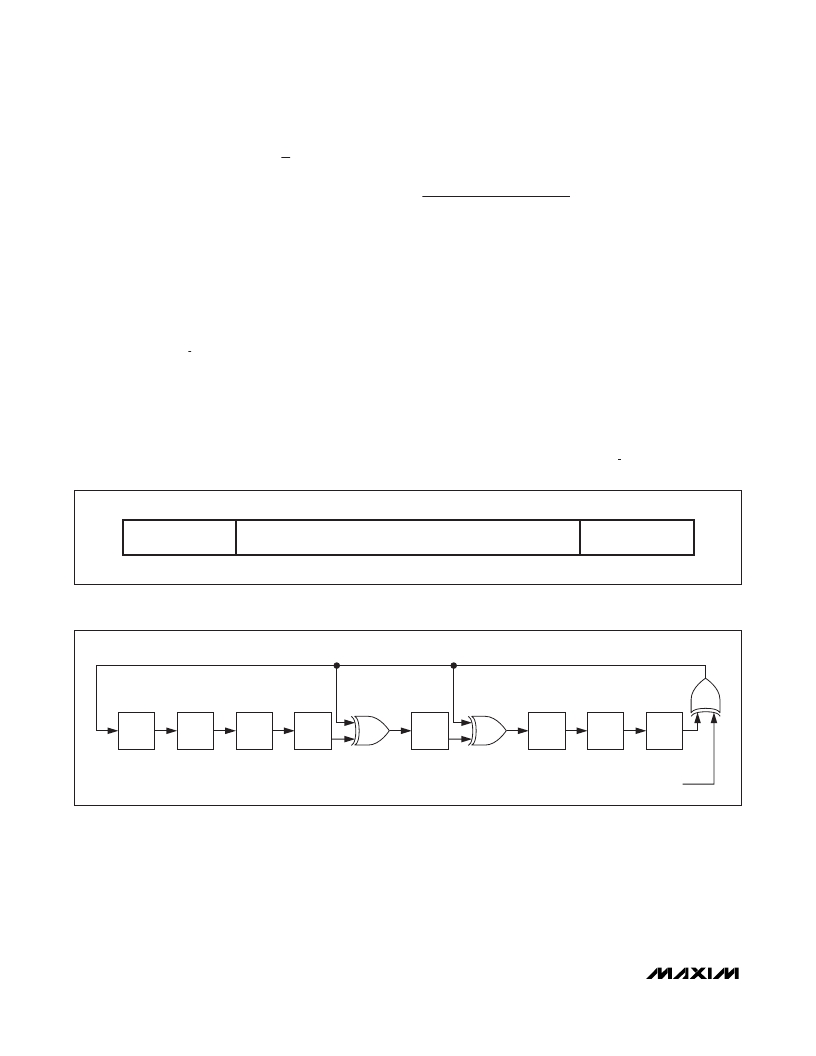

�The� 1-Wire� CRC� is� generated� using� a� polynomial� gen-�

�erator� consisting� of� a� shift� register� and� XOR� gates� as�

�shown� in� Figure� 3.� The� polynomial� is� X� 8� +� X� 5� +� X� 4� +� 1.�

�Additional� information� about� the� 1-Wire� Cyclic�

�Redundancy� Check� (CRC)� is� available� in� Application�

�Note� 27:� Understanding� and� Using� Cyclic� Redundancy�

�Checks� with� Maxim� iButton� Products.�

�The� shift� register� bits� are� initialized� to� 0.� Then� starting�

�with� the� least� significant� bit� of� the� family� code,� one� bit�

�at� a� time� is� shifted� in.� After� the� 8th� bit� of� the� family� code�

�has� been� entered,� the� serial� number� is� entered.� After�

�the� 48th� bit� of� the� serial� number� has� been� entered,� the�

�shift� register� contains� the� CRC� value.� Shifting� in� the� 8�

�bits� of� CRC� returns� the� shift� register� to� all� 0s.�

�MSB�

�1-Wire� Bus� System�

�The� 1-Wire� bus� is� a� system� that� has� a� single� bus� master�

�and� one� or� more� slaves.� In� all� instances,� the� DS1990R�

�is� a� slave� device.� The� bus� master� is� typically� a� micro-�

�controller� or� PC.� For� small� configurations,� the� 1-Wire�

�communication� signals� can� be� generated� under� soft-�

�ware� control� using� a� single� port� pin.� Alternatively,� the�

�DS2480B� 1-Wire� line� driver� chip� or� serial-port� adapters�

�based� on� this� chip� (DS9097U� series)� can� be� used.� This�

�simplifies� the� hardware� design� and� frees� the� micro-�

�processor� from� responding� in� real� time.� The� discussion�

�of� this� bus� system� is� broken� down� into� three� topics:�

�hardware� configuration,� transaction� sequence,� and�

�1-Wire� signaling� (signal� types� and� timing).� The� 1-Wire�

�protocol� defines� bus� transactions� in� terms� of� the� bus�

�state� during� specific� time� slots� that� are� initiated� on� the�

�falling� edge� of� sync� pulses� from� the� bus� master.� For� a�

�more� detailed� protocol� description,� refer� to� Chapter� 4� of�

�the� Application� Note� 937:� Book� of� iButton� Standards.�

�LSB�

�8-BIT�

�CRC� CODE�

�48-BIT� SERIAL� NUMBER�

�8-BIT� FAMILY� CODE�

�(01h)�

�MSB�

�LSB� MSB�

�LSB� MSB�

�LSB�

�Figure� 2.� 64-Bit� Lasered� ROM�

�POLYNOMIAL� =� X� 8� +� X� 5� +� X� 4� +� 1�

�1ST�

�STAGE�

�2ND�

�STAGE�

�3RD�

�STAGE�

�4TH�

�STAGE�

�5TH�

�STAGE�

�6TH�

�STAGE�

�7TH�

�STAGE�

�8TH�

�STAGE�

�X� 0�

�X� 1�

�X� 2�

�X� 3�

�X� 4�

�X� 5�

�X� 6�

�X� 7�

�X� 8�

�INPUT� DATA�

�Figure� 3.� 1-Wire� CRC� Generator�

�4�

�_______________________________________________________________________________________�

�相关PDF资料 |

PDF描述 |

|---|---|

| DS1993L-F5+ | IBUTTON MEMORY 4KBit F5 |

| DS1995L-F5+ | IBUTTON MEMORY 16KBit F5 |

| DS1996L-F5+ | IBUTTON MEMORY 64KBit F5 |

| DS9092K# | KIT IBUTTON STARTER |

| DS9502P+T&R | DIODE ESD PROTECTION 6-TSOC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS1990R-F5# | 功能描述:序列号注册 Serial Number iButton RoHS:否 制造商:Maxim Integrated 数据总线宽度: 电源电压-最大: 电源电压-最小: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: |

| DS1990R-F5+W | 功能描述:序列号注册 RoHS:否 制造商:Maxim Integrated 数据总线宽度: 电源电压-最大: 电源电压-最小: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: |

| DS1990-序列号IBUTTON | 制造商:未知厂家 制造商全称:未知厂家 功能描述: |

| DS1991 | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:MultiKey iButton |

| DS1991L | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

发布紧急采购,3分钟左右您将得到回复。