- 您现在的位置:买卖IC网 > PDF目录3760 > DS2186S+ (Maxim Integrated Products)IC TRANSMIT LINE INTERFC 20SOIC PDF资料下载

参数资料

| 型号: | DS2186S+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 6/11页 |

| 文件大小: | 0K |

| 描述: | IC TRANSMIT LINE INTERFC 20SOIC |

| 标准包装: | 37 |

| 类型: | 线路驱动器,发射器 |

| 驱动器/接收器数: | 1/0 |

| 规程: | T1/CEPT |

| 电源电压: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 20-SOIC W |

| 包装: | 管件 |

| 产品目录页面: | 1429 (CN2011-ZH PDF) |

DS2186

022798 4/11

The shape of the “pre–emphasized” T1 waveform is

controlled

by

inputs

LEN0,

LEN1,

and

LEN2

(TCLKSEL=0). These control inputs allow the user to

select the appropriate output pulse shape to meet

DSX–1 or CSU templates over a wide variety of cable

types and lengths. Those cable types include ABAM,

PIC, and PULP.

The CEPT mode is enabled when TCLKSEL=1. Only

one output pulse shape is available in the CEPT mode;

inputs LEN0, LEN1 and LEN2 can be any state except

all zeros.

The line coupling transformer also contributes to the

pulse shape seen at the cross–connect point. Trans-

formers for both T1 and CEPT applications must be

1:1.35.

The wave shaping circuitry does not contribute signifi-

cantly to output jitter (less than 0.01 UIpp broadband).

Output jitter will be dominated by the jitter on TCLK or

LCLK. TCLK and LCLK need only be accurate in fre-

quency, not duty cycle.

LINE DRIVERS

The on–chip differential line drivers interface directly to

the output transformer. To optimize device perform-

ance, length of the TTIP and TRING traces should be

minimized and isolated from neighboring interconnect.

FAULT PROTECTION

The line drivers are fault–protected and will withstand a

shorted transformer secondary (or primary) without

damage. Inputs MTIP and MRING are normally tied to

TTIP and TRING to provide fault monitoring capability.

Output LF will transition low if 192 TCLK cycles occur

without a one occurring at MTIP or MRING. LF will tri–

state on the next one occurrence or two TCLK periods

later, whichever is greater.

The threshold of MTIP and MRING varies with the line

type selected at LEN0, LEN1 and LEN2. This insures

detection of the lowest level zero to one transition (–15

dB buildout) as it occurs on TTIP and TRING.

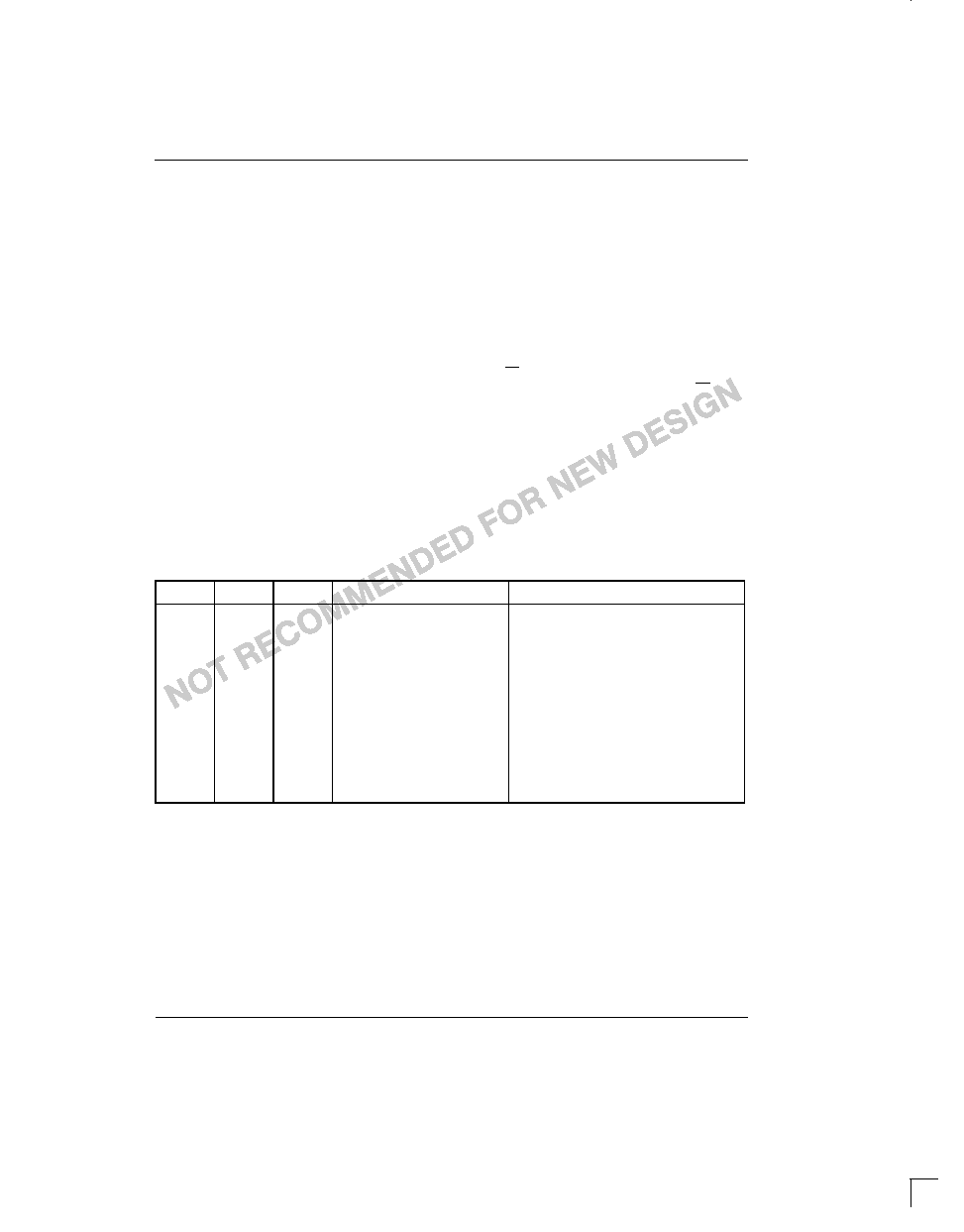

T1 LINE LENGTH SELECTION Table 2

LEN2

LEN1

LEN0

OPTION SELECTED

APPLICATION

0

Test mode

Do not use

0

1

–7.5 dB buildout

T1 CSU

0

1

0

–15 dB buildout

T1 CSU

0

1

0 dB buildout,

0 – 133 feet

T1 CSU, DSX–1 Cross connect

1

0

133 – 266 feet

DSX–1 Cross connect

1

0

1

266 – 399 feet

DSX–1 Cross connect

1

0

399 – 533 feet

DSX–1 Cross connect

1

533 – 655 feet

DSX–1 Cross connect

NOTE:

1. The LEN0, LEN1 and LEN2 inputs control T1 output waveshapes when TCLKSEL=0. The G.703 (CEPT) template

is selected when TCLKSEL=1 and LEN0, LEN1, and LEN2 are at any state except all zeros.

相关PDF资料 |

PDF描述 |

|---|---|

| DS2186S | IC TRANSMIT LINE INTERFC 20-SOIC |

| DS275 | IC TXRX LINE-PWR RS232 8-DIP |

| PCKV857DGG,518 | IC 1:10 2.5V PLL CLK-DRVR48TSSOP |

| PCKV857DGG,512 | IC 1:10 2.5V PLL CLK-DRVR48TSSOP |

| PCKV857EV,151 | IC 1:10 2.5V PLL CLK-DRVR48TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS2186S/T&R | 制造商:Maxim Integrated Products 功能描述:TRANSMIT LINE INTERFACE SOIC TRL - Tape and Reel 制造商:Maxim Integrated Products 功能描述:IC TRANSMIT LINE INTERFC 20-SOIC |

| DS2186S/T&R | 功能描述:IC TRANSMIT LINE INTERFC 20-SOIC RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:25 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:4.5 V ~ 5.5 V 安装类型:通孔 封装/外壳:16-DIP(0.300",7.62mm) 供应商设备封装:16-PDIP 包装:管件 |

| DS2186S+ | 功能描述:网络控制器与处理器 IC Transmit Line Interface RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS2186SN | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CEPT/T1 Interface |

| DS2187 | 功能描述:网络控制器与处理器 IC Receive Line Interface RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。