- 您现在的位置:买卖IC网 > PDF目录16263 > DS21Q352DK (Maxim Integrated Products)KIT DESIGN FOR DS21Q352 PDF资料下载

参数资料

| 型号: | DS21Q352DK |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 11/13页 |

| 文件大小: | 0K |

| 描述: | KIT DESIGN FOR DS21Q352 |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 主要目的: | 电信,调帧器和线路接口装置(LIU) |

| 已用 IC / 零件: | DS21Q352 |

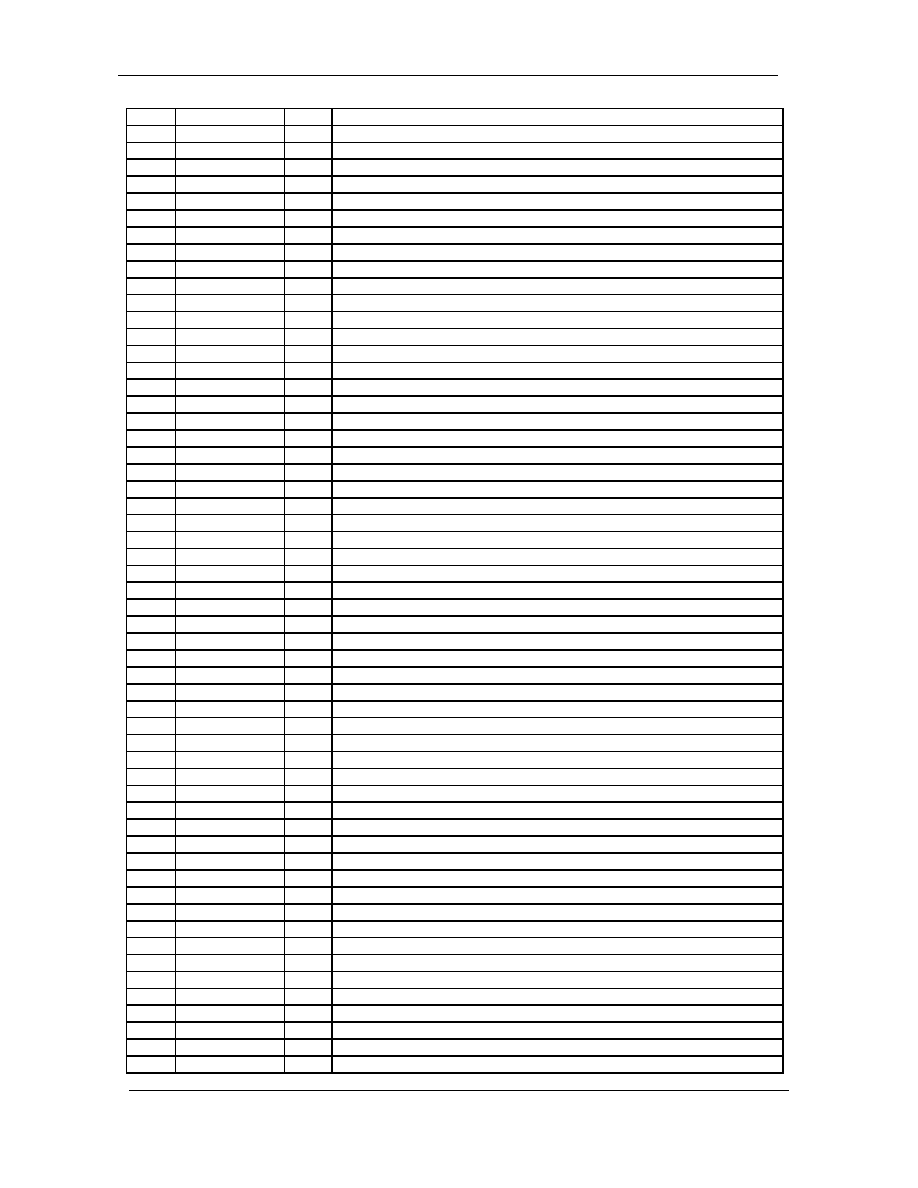

DALLAS SEMICONDUCTOR

DS21Q352/DS21Q552/DS21Q354/DS21Q554 Preliminary Data Sheet

December 29, 1998

7

A17

DVSS2

–

Digital Signal Ground.

A20

DVSS2

–

Digital Signal Ground.

B11

DVSS2

–

Digital Signal Ground.

C13

DVSS2

–

Digital Signal Ground.

A5

DVSS3

–

Digital Signal Ground.

B7

DVSS3

–

Digital Signal Ground.

B9

DVSS3

–

Digital Signal Ground.

C3

DVSS3

–

Digital Signal Ground.

H20

DVSS4

–

Digital Signal Ground

L20

DVSS4

–

Digital Signal Ground

N17

DVSS4

–

Digital Signal Ground

U13

DVSS4

–

Digital Signal Ground

U1

INT*

O

Interrupt for all four SCTs.

Y15

JTCLK

I

JTAG Clock.

N1

JTDI

I

JTAG Data Input.

H18

JTDO2

O

JTAG Data Output from SCT2.

V17

JTDO3

O

JTAG Data Output from SCT3.

V19

JTDO4

O

JTAG Data Output from SCT4.

W13

JTMS

I

JTAG Test Mode Select.

V18

JTRST*

I

JTAG Reset.

K2

LIUC

I

Line Interface Connect for all Four SCTs.

T1

MCLK1

I

Master Clock for SCT1 and SCT3.

W20

MCLK2

I

Master Clock for SCT2 and SCT4.

U10

MUX

I

Mux Bus Select.

M2

RCHBLK1

O

Receive Channel Block for SCT1.

G17

RCHBLK2

O

Receive Channel Block for SCT2.

G4

RCHBLK3

O

Receive Channel Block for SCT3.

Y12

RCHBLK4

O

Receive Channel Block for SCT4.

J1

RCHCLK1

O

Receive Channel Clock for SCT1.

D14

RCHCLK2

O

Receive Channel Clock for SCT2.

F3

RCHCLK3

O

Receive Channel Clock for SCT3.

U14

RCHCLK4

O

Receive Channel Clock for SCT4.

N3

RCLK1

O

Receive Clock Output from the Framer on SCT1.

B13

RCLK2

O

Receive Clock Output from the Framer on SCT2.

E3

RCLK3

O

Receive Clock Output from the Framer on SCT3.

M18

RCLK4

O

Receive Clock Output from the Framer on SCT4.

M4

RCLKI1

I

Receive Clock Input for the LIU on SCT1.

A15

RCLKI2

I

Receive Clock Input for the LIU on SCT2.

A4

RCLKI3

I

Receive Clock Input for the LIU on SCT3.

R17

RCLKI4

I

Receive Clock Input for the LIU on SCT4.

M3

RCLKO1

O

Receive Clock Output from the LIU on SCT1.

C14

RCLKO2

O

Receive Clock Output from the LIU on SCT2.

B4

RCLKO3

O

Receive Clock Output from the LIU on SCT3.

T17

RCLKO4

O

Receive Clock Output from the LIU on SCT4.

N2

RD*(DS*)

I

Read Input (Data Strobe)

K4

RFSYNC1

O

Receive Frame Sync (before the receive elastic store) for SCT1.

D17

RFSYNC2

O

Receive Frame Sync (before the receive elastic store) for SCT2.

A2

RFSYNC3

O

Receive Frame Sync (before the receive elastic store) for SCT3.

V14

RFSYNC4

O

Receive Frame Sync (before the receive elastic store) for SCT4.

F1

RLCLK1

O

Receive Link Clock for SCT1.

A12

RLCLK2

O

Receive Link Clock for SCT2.

D3

RLCLK3

O

Receive Link Clock for SCT3.

K18

RLCLK4

O

Receive Link Clock for SCT4.

G2

RLINK1

O

Receive Link Data for SCT1.

A13

RLINK2

O

Receive Link Data for SCT2.

A3

RLINK3

O

Receive Link Data for SCT3.

U12

RLINK4

O

Receive Link Data for SCT4.

相关PDF资料 |

PDF描述 |

|---|---|

| MC34064P-5RAG | IC SENSOR UNDERVOLTAGE TO-92 |

| M3AGK-2006R | IDC CABLE - MSC20K/MC20M/MCS20K |

| SLPX331M180A1P3 | CAP ALUM 330UF 180V 20% SNAP |

| SLP331M160A1P3 | CAP ALUM 330UF 160V 20% SNAP |

| SLPX271M200A1P3 | CAP ALUM 270UF 200V 20% SNAP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS21Q352N | 功能描述:网络控制器与处理器 IC 3.3/5V Quad T1/E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21Q354 | 功能描述:网络控制器与处理器 IC 3.3/5V Quad T1/E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21Q354B | 功能描述:网络控制器与处理器 IC 3.3/5V Quad T1/E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21Q354B+ | 功能描述:网络控制器与处理器 IC 3.3/5V Quad T1/E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21Q354BN | 功能描述:网络控制器与处理器 IC 3.3/5V Quad T1/E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。