- 您现在的位置:买卖IC网 > PDF目录4573 > DS2401-SL+T&R (Maxim Integrated Products)IC SILICON SERIAL NUMBER TO-92 PDF资料下载

参数资料

| 型号: | DS2401-SL+T&R |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 2/11页 |

| 文件大小: | 0K |

| 描述: | IC SILICON SERIAL NUMBER TO-92 |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,000 |

| 类型: | 硅序列号 |

| 应用: | PCB,网络节点,设备识别/注册 |

| 安装类型: | 通孔 |

| 封装/外壳: | TO-226-3、TO-92-3(TO-226AA)成形引线 |

| 供应商设备封装: | TO-92-3 |

| 包装: | 带卷 (TR) |

DS2401

NOTES:

1) All voltages are referenced to ground.

2) VPUP= external pullup voltage.

3) Input load is to ground.

4) An additional reset or communication sequence cannot begin until the reset high time has expired.

5) Read data setup time refers to the time the host must pull the 1-Wire bus low to read a bit. Data is

guaranteed to be valid within 1s of this falling edge and will remain valid for 14s minimum (15s

total from falling edge on 1-Wire bus).

6) VIH is a function of the external pullup resistor and VPUP.

7) 30 nanocoulombs per 72 time slots at 5.0V.

8) At VPUP= 5.0V with a 5k pullup to VPUP and a maximum time slot of 120s.

9) Capacitance on the I/O pin could be 800pF when power is first applied. If a 5k resistor is used to

pullup the I/O line to VPUP, 5s after power has been applied the parasite capacitance will not affect

normal communications.

10) The reset low time (tRSTL) should be restricted to a maximum of 960s, to allow interrupt signaling,

otherwise it could mask or conceal interrupt pulses if this device is used in parallel with a DS2404 or

DS1994.

11) The optimal sampling point for the master is as close as possible to the end time of the tRDV period

without exceeding tRDV. For the case of a Read-One Time slot, this maximizes the amount of time for

the pullup resistor to recover to a high level. For a Read-Zero Time slot, it ensures that a read will

occur before the fastest 1-Wire device(s) releases the line.

12) The duration of the low pulse sent by the master should be a minimum of 1μs with a maximum value

as short as possible to allow time for the pullup resistor to recover the line to a high level before the

1-Wire device samples in the case of a Write-One Time or before the master samples in the case of a

Read-One Time.

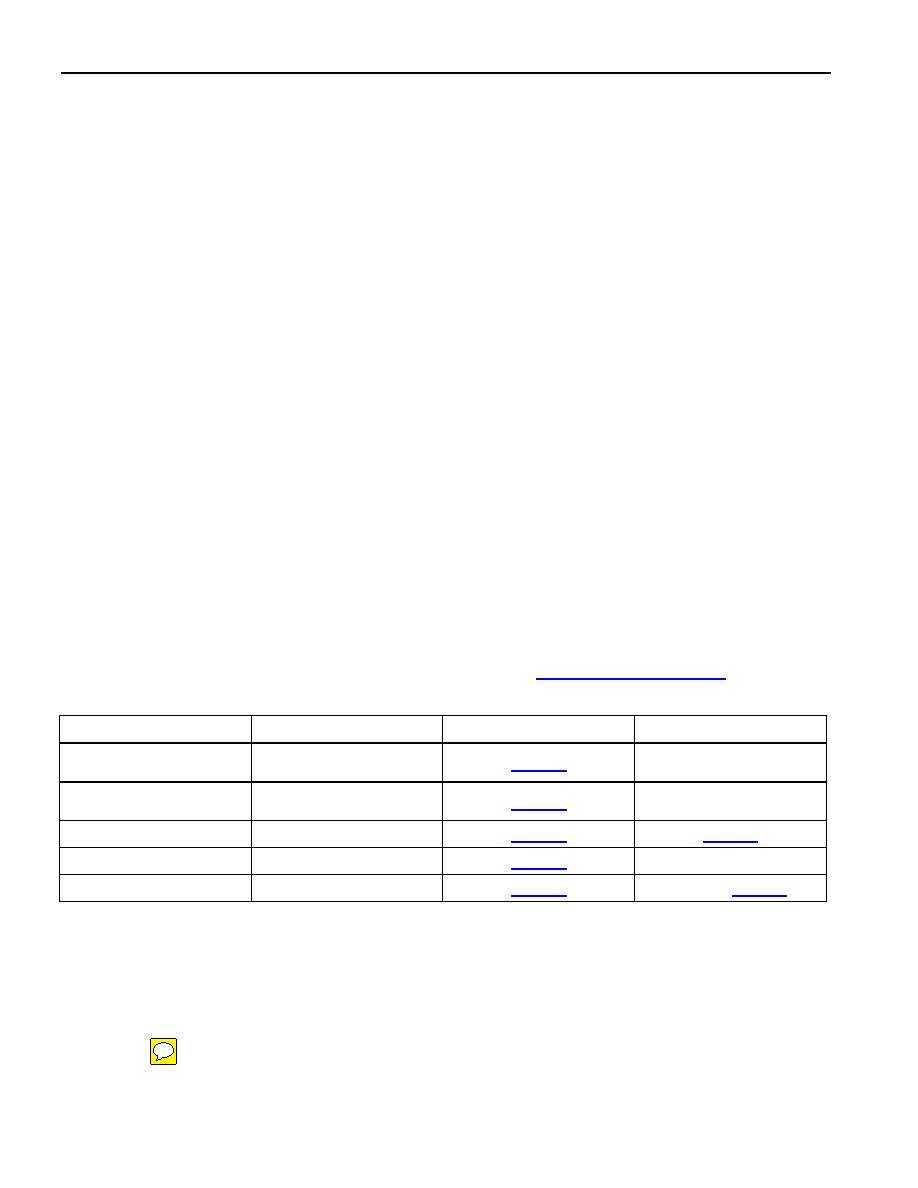

PACKAGE INFORMATION

For the latest package outline information and land patterns (footprints), go to www.maxim-ic.com/packages. Note that a “+”,

“#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the

drawing pertains to the package regardless of RoHS status.

PACKAGE TYPE

PACKAGE CODE

OUTLINE NO.

LAND PATTERN NO.

3 TO-92

(straight leads)

Q3+1

—

3 TO-92

(formed leads)

Q3+4

—

6 TSOC

D6+1

4 SOT-223

K3+1

—

2 Flip Chip

BF211#1

Refer to

相关PDF资料 |

PDF描述 |

|---|---|

| DS2401+T&R | IC SILICON SERIAL NUMBER TO-92 |

| MAX1329BETL+T | IC DAS 12BIT 300KSPS 40-TQFN-EP |

| DS1402-BP8+ | CABLE 8' BUTTON TO PROBE |

| MAX5426BEUD+ | IC INSTR AMP PROGR PREC 14-TSSOP |

| MAX5426AEUD+T | IC INSTR AMP PROGR PREC 14-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS2401T | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:Silicon Serial Number |

| DS2401T-SL | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:Silicon Serial Number |

| DS2401V | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:Silicon Serial Number |

| DS2401X1 | 功能描述:序列号注册 Silicon Serial Number RoHS:否 制造商:Maxim Integrated 数据总线宽度: 电源电压-最大: 电源电压-最小: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: |

| DS2401X1#U | 功能描述:序列号注册 Silicon Serial Number RoHS:否 制造商:Maxim Integrated 数据总线宽度: 电源电压-最大: 电源电压-最小: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: |

发布紧急采购,3分钟左右您将得到回复。