- 您现在的位置:买卖IC网 > PDF目录1916 > DS33R11+CJ2 (Maxim Integrated Products)IC ETH TXRX T1/E1/J1 256-BGA PDF资料下载

参数资料

| 型号: | DS33R11+CJ2 |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 190/344页 |

| 文件大小: | 0K |

| 描述: | IC ETH TXRX T1/E1/J1 256-BGA |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 90 |

| 类型: | 收发器 |

| 规程: | T1/E1/J1 |

| 电源电压: | 1.8V, 3.3V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-BBGA |

| 供应商设备封装: | 256-BGA(27x27) |

| 包装: | 托盘 |

| 其它名称: | 90-33R11+C01 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页当前第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页第215页第216页第217页第218页第219页第220页第221页第222页第223页第224页第225页第226页第227页第228页第229页第230页第231页第232页第233页第234页第235页第236页第237页第238页第239页第240页第241页第242页第243页第244页第245页第246页第247页第248页第249页第250页第251页第252页第253页第254页第255页第256页第257页第258页第259页第260页第261页第262页第263页第264页第265页第266页第267页第268页第269页第270页第271页第272页第273页第274页第275页第276页第277页第278页第279页第280页第281页第282页第283页第284页第285页第286页第287页第288页第289页第290页第291页第292页第293页第294页第295页第296页第297页第298页第299页第300页第301页第302页第303页第304页第305页第306页第307页第308页第309页第310页第311页第312页第313页第314页第315页第316页第317页第318页第319页第320页第321页第322页第323页第324页第325页第326页第327页第328页第329页第330页第331页第332页第333页第334页第335页第336页第337页第338页第339页第340页第341页第342页第343页第344页

DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

27 of 344

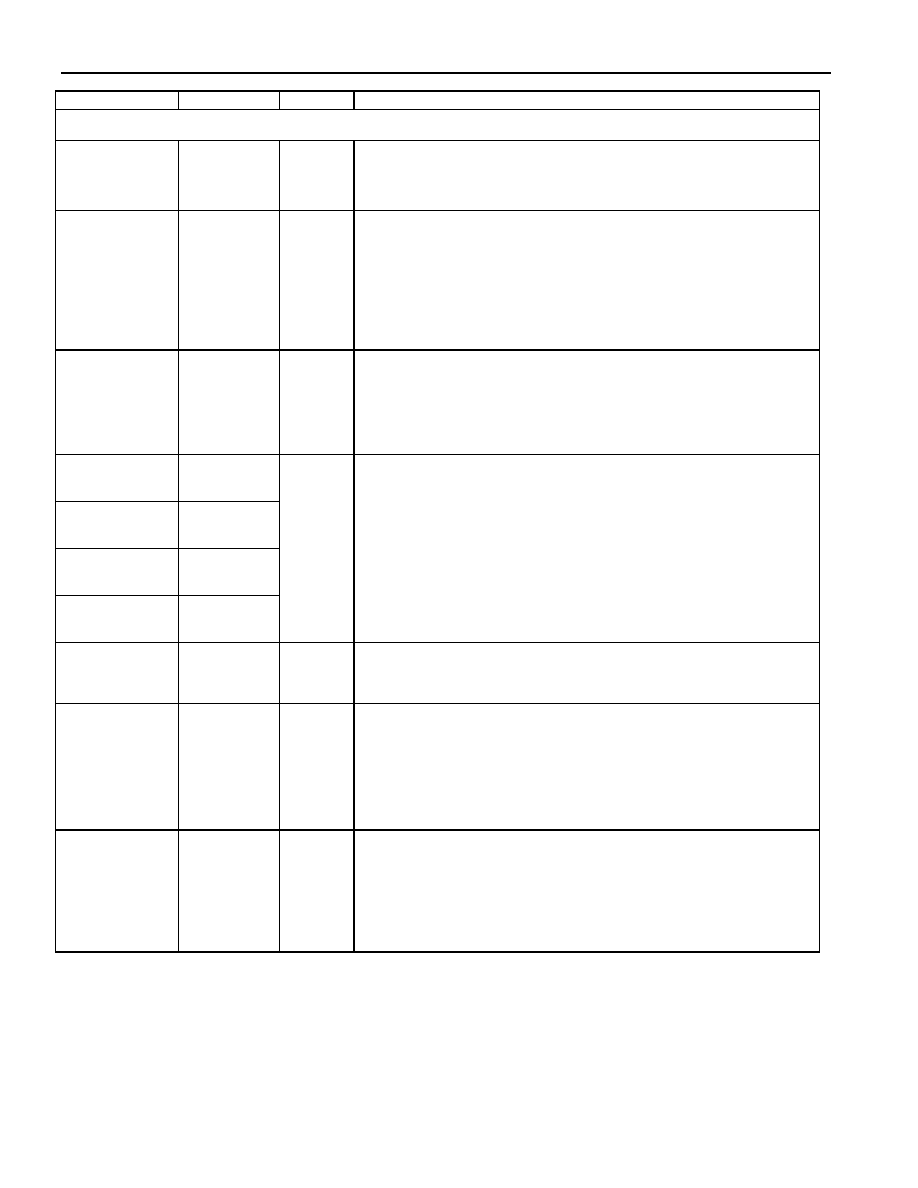

NAME

PIN

TYPE

FUNCTION

MII/RMII PHY PORT

COL_DET

N18

I

Collision Detect (MII): Asserted by the MAC PHY to indicate that a

collision is occurring. In DCE Mode this signal should be connected

to ground. This signal is only valid in half duplex mode, and is

ignored in full duplex mode.

RX_CRS/

CRS_DV

M19

I

Receive Carrier Sense (MII): Should be asserted (high) when data

from the PHY (RXD[3:0) is valid. For each clock pulse 4 bits arrive

from the PHY. Bit 0 is the least significant bit. In DCE mode,

connect to VDD.

Carrier Sense/Receive Data Valid (RMII): This signal is asserted

(high) when data is valid from the PHY. For each clock pulse 2 bits

arrive from the PHY. In DCE mode, this signal must be grounded.

RX_CLK

M20

IO

Receive Clock (MII): Timing reference for RX_DV, RX_ERR and

RXD[3:0], which are clocked on the rising edge. RX_CLK frequency

is 25MHz for 100Mbit/s operation and 2.5MHz for 10Mbit/s

operation. In DTE mode, this is a clock input provided by the PHY.

In DCE mode, this is an output derived from REF_CLK providing

2.5MHz (10Mbit/s operation) or 25MHz (100Mbit/s operation).

RXD[0]

L18

RXD[1]

L19

RXD[2]

L20

RXD[3]

M18

O

Receive Data 0 through 3 (MII): Four bits of received data,

sampled synchronously with the rising edge of RX_CLK. For every

clock cycle, the PHY transfers 4 bits to the DS33R11. RXD[0] is the

least significant bit of the data. Data is not considered valid when

RX_DV is low.

Receive Data 0 through 1 (RMII): Two bits of received data,

sampled synchronously with REF_CLK with 100Mbit/s mode.

Accepted when CRS_DV is asserted. When configured for

10Mbit/s mode, the data is sampled once every 10 clock periods.

RX_DV

K19

I

Receive Data Valid (MII): This active high signal indicates valid

data from the PHY. The data RXD is ignored if RX_DV is not

asserted high.

RX_ERR

K18

I

Receive Error (MII): Asserted by the MAC PHY for one or more

RX_CLK periods indicating that an error has occurred. Active High

indicates Receive code group is invalid. If CRS_DV is low,

RX_ERR has no effect. This is synchronous with RX_CLK. In DCE

mode, this signal must be grounded.

Receive Error (RMII): Signal is synchronous to REF_CLK.

TX_CLK

H19

IO

Transmit Clock (MII): Timing reference for TX_EN and TXD[3:0].

The TX_CLK frequency is 25MHz for 100Mbit/s operation and

2.5MHz for 10Mbit/s operation.

In DTE mode, this is a clock input provided by the PHY. In DCE

mode, this is an output derived from REF_CLK providing 2.5MHz

(10Mbit/s operation) or 25MHz (100Mbit/s operation).

相关PDF资料 |

PDF描述 |

|---|---|

| DS33R41+ | IC TXRX ETHERNET MAP 400-BGA |

| DS33W11DK+ | IC MAPPING ETHERNET 256-CSBGA |

| DS33Z11+UNUSED | IC ETHERNET MAPPER 169-CSBGA |

| DS33Z44+ | IC MAPPER ETHERNET 256CSBGA |

| DS33ZH11+ | IC MAPPER ETHERNET 100CSBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS33R11DK | 功能描述:以太网开发工具 DS33R11 Dev Kit RoHS:否 制造商:Micrel 产品:Evaluation Boards 类型:Ethernet Transceivers 工具用于评估:KSZ8873RLL 接口类型:RMII 工作电源电压: |

| DS33R41 | 功能描述:网络控制器与处理器 IC Inv-Mult Enet Mapper w/Quad T1/E1/J1 Trx RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS33R41+ | 功能描述:网络控制器与处理器 IC Inv-Mult Enet Mapper w/Quad T1/E1/J1 Trx RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS33W11+ | 功能描述:网络控制器与处理器 IC Ethernet Over PDH Mapping Devices RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS33W11DK+ | 功能描述:以太网开发工具 1/1 E-Net - PDH Design Kit RoHS:否 制造商:Micrel 产品:Evaluation Boards 类型:Ethernet Transceivers 工具用于评估:KSZ8873RLL 接口类型:RMII 工作电源电压: |

发布紧急采购,3分钟左右您将得到回复。