- 您现在的位置:买卖IC网 > PDF目录10589 > EL1881CSZ-T7A (Intersil)IC VIDEO SYNC SEPARATOR 8SOIC PDF资料下载

参数资料

| 型号: | EL1881CSZ-T7A |

| 厂商: | Intersil |

| 文件页数: | 2/13页 |

| 文件大小: | 0K |

| 描述: | IC VIDEO SYNC SEPARATOR 8SOIC |

| 标准包装: | 250 |

| 类型: | 同步分离器 |

| 应用: | 驱动器,通信,PCMCIA |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 8-SO |

| 包装: | 带卷 (TR) |

10

FN7018.2

September 15, 2011

that has a duty cycle of about 15%. Vertical Sync is clocked

out of the EL1881 on the first rising edge during the vertical

serration phase. In the absence of vertical serration pulses,

a vertical sync pulse will be forced out after the vertical sync

default delay time, approximately 60s after the last falling

edge of the vertical equalizing phase for RSET = 681kΩ.

Odd/Even

Because a typical television picture is composed of two

interlaced fields, there is an odd field that includes all the

odd lines, and an even field that consists of the even lines.

This odd/even field information is decoded by the EL1881

during the end of picture information and the beginning of

vertical information. The odd/even circuit includes a

T-flip-flop that is reset during full horizontal lines, but not

during half lines or vertical equalization pulses. The

T-flip-flop is clocked during each falling edge of these

half-period pulses. Even fields will toggle until a low state is

clocked to the odd/even pin 7 at the beginning of vertical

sync, and odd fields will cause a high state to be clocked to

the odd/even pin at the start of the next vertical sync pulse.

Odd/even can be ignored if using non-interlaced video, as

there is no change in timing from one field to the next.

RSET

An external RSET resistor, connected from RSET pin 6 to

ground, produces a reference current that is used internally

as the timing reference for vertical sync width, vertical sync

default delay, burst gate delay and burst width. Decreasing

the value of RSET increases the reference current, which in

turn decreases reference times and pulse widths. A higher

frequency video input necessitates a lower RSET value.

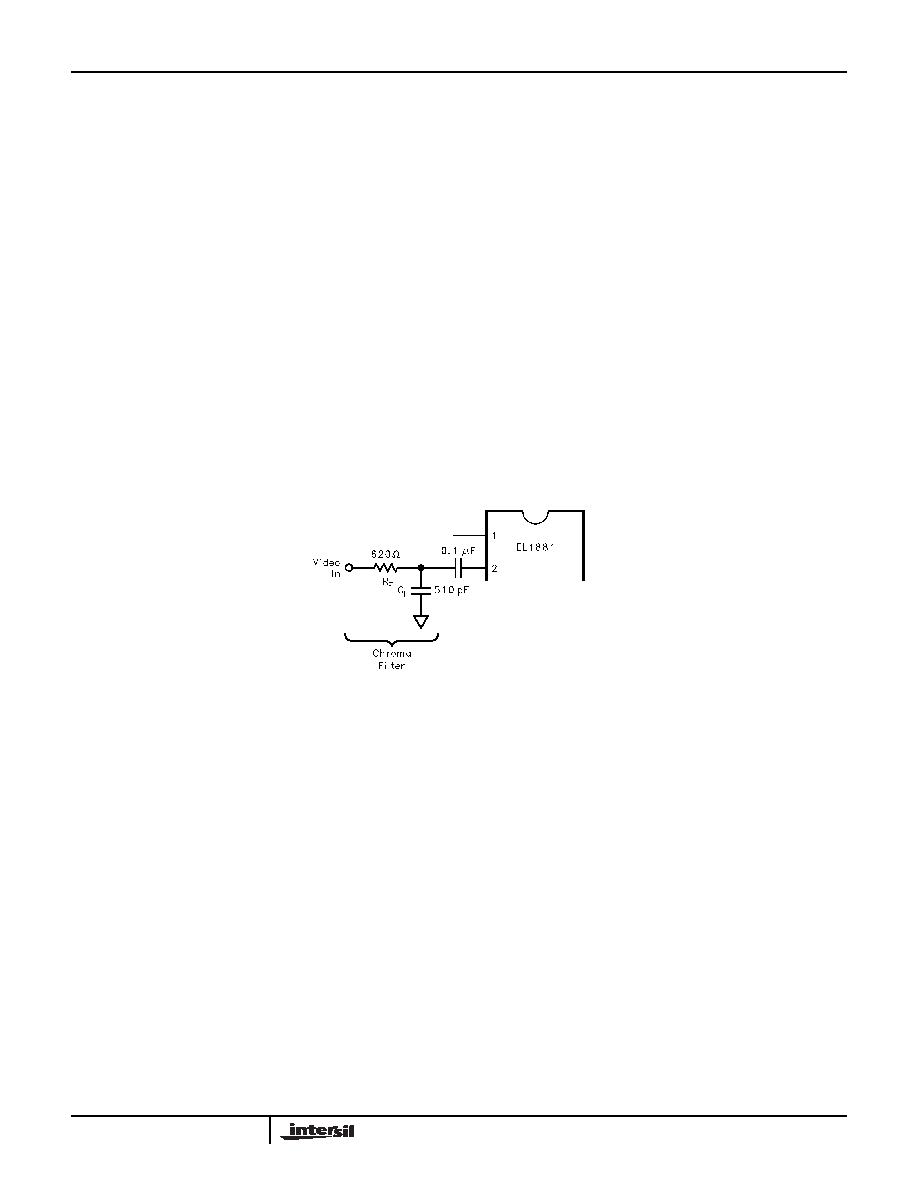

Chroma Filter

A chroma filter is suggested to increase the S/N ratio of the

incoming video signal. Use of the optional chroma filter is

shown in Figure 23. It can be implemented very simply and

inexpensively with a series resistor of 620

Ω and a parallel

capacitor of 500pF, which gives a single pole roll-off

frequency of about 500kHz. This sufficiently attenuates the

3.58MHz (NTSC) or 4.43MHz (PAL) color burst signal, yet

passes the approximately 15kHz sync signals without

appreciable attenuation. A chroma filter will increase the

propagation delay from the composite input to the outputs.

FIGURE 23.

EL1881

相关PDF资料 |

PDF描述 |

|---|---|

| HI3-574AKN-5Z | IC ADC 12BIT 40KSPS 28-PDIP |

| PT06A-8-2P | CONN PLUG 2 POS STRAIGHT W/PINS |

| EL1883ISZ-T7 | IC VID SYNC SEPARATOR HORZ 8SOIC |

| EL1883ISZ-T13 | IC VID SYNC SEPARATOR HORZ 8SOIC |

| FMS6406CSX | IC FILTER S-VIDEO DUAL 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EL1882C | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Sync Separator w/50% Slice, AGC |

| EL1882CN | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Sync Separator w/50% Slice, AGC |

| EL1882CS | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Sync Separator w/50% Slice, AGC |

| EL1883 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Sync Separator with Horizontal Output |

| EL1883_06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Sync Separator with Horizontal Output |

发布紧急采购,3分钟左右您将得到回复。