- 您现在的位置:买卖IC网 > PDF目录10624 > EL1881CSZ (Intersil)IC VIDEO SYNC SEPARATOR 8SOIC PDF资料下载

参数资料

| 型号: | EL1881CSZ |

| 厂商: | Intersil |

| 文件页数: | 13/13页 |

| 文件大小: | 0K |

| 描述: | IC VIDEO SYNC SEPARATOR 8SOIC |

| 标准包装: | 97 |

| 类型: | 同步分离器 |

| 应用: | 驱动器,通信,PCMCIA |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 8-SOIC |

| 包装: | 管件 |

| 产品目录页面: | 1247 (CN2011-ZH PDF) |

9

FN7018.2

September 15, 2011

Applications Information

Video In

Figure 24 shows a “Simplified Block Diagram” on page 11.

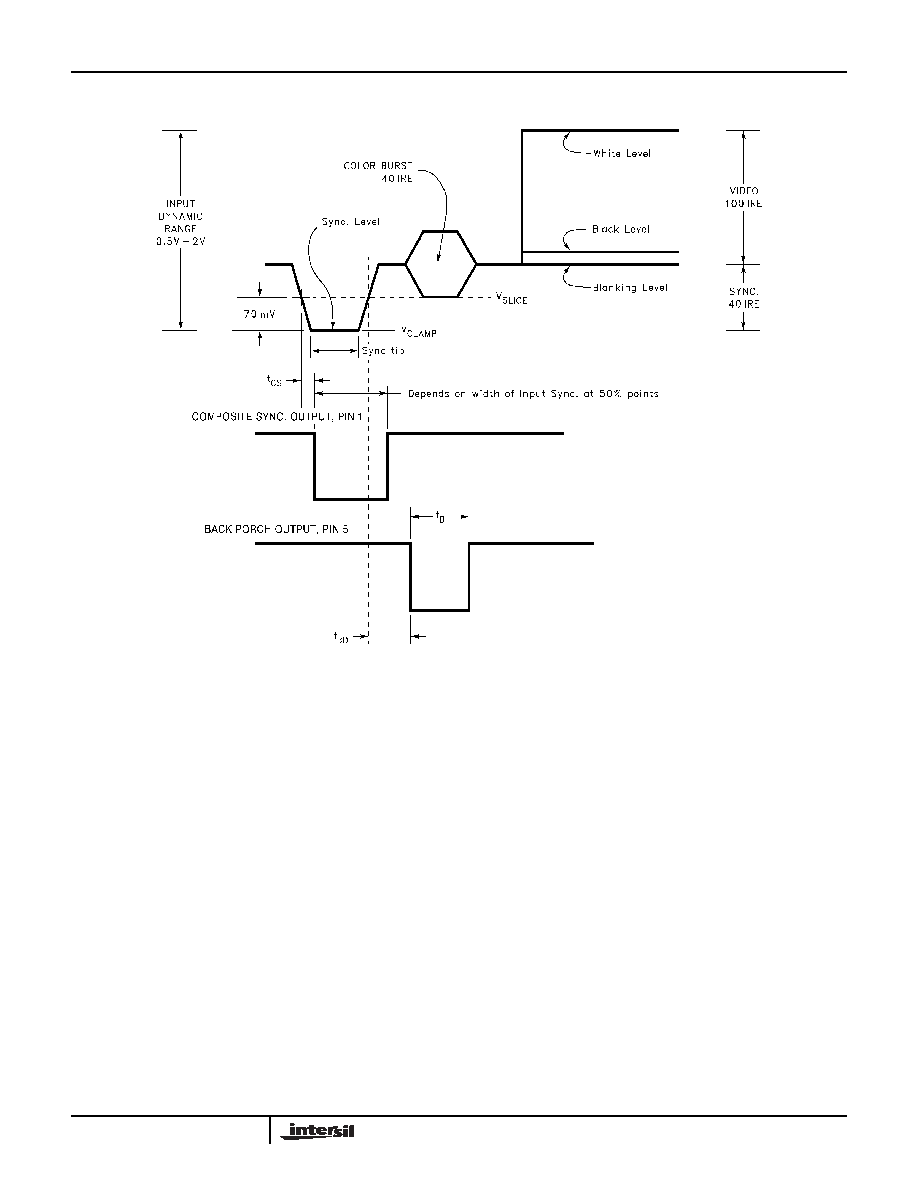

An AC-coupled video signal is input to Video In pin 2 via, C1

nominally 0.1F. Clamp charge current will prevent the

signal on pin 2 from going any more negative than Sync Tip

Ref, about 1.5V. This charge current is nominally about 1mA.

A clamp discharge current of about 10A is always

attempting to discharge C1 to Sync Tip Ref, thus charge is

lost between sync pulses that must be replaced during sync

pulses. The droop voltage that will occur can be calculated

from It = CV, where V is the droop voltage, I is the discharge

current, t is the time between sync pulses

(sync period - sync tip width), and C is C1.

An NTSC video signal has a horizontal frequency of

15.73kHz, and a sync tip width of 4.7s. This gives a period

of 63.6s and a time t = 58.9s. The droop voltage will then

be V = 5.9mV. This is < 2% of a nominal sync tip amplitude

of 286mV. The charge represented by this droop is replaced

in a time given by t = CV/I, where I = clamp charge current =

1mA. Here t = 590ns, about 12% of the sync pulse width of

4.7s. It is important to choose C1 large enough so that the

droop voltage does not approach the switching threshold of

the internal comparator.

Fixed Gain Buffer

The clamped video signal then passes to the fixed gain

buffer which places the sync slice level at the equivalent

level of 70mV above sync tip. The output of this buffer is

presented to the comparator, along with the slice reference.

The comparator output is level shifted and buffered to TTL

levels, and sent out as Composite Sync to pin 1.

Burst

A low-going Burst pulse follows each rising edge of sync,

and lasts approximately 3.5s for an RSET of 681kΩ.

Vertical Sync

A low-going Vertical Sync pulse is output during the start of

the vertical cycle of the incoming video signal. The vertical

cycle starts with a pre-equalizing phase of pulses with a duty

cycle of about 93%, followed by a vertical serration phase

FIGURE 22. STANDARD VERTICAL TIMING

Expanded Timing Diagrams (Continued)

EL1881

相关PDF资料 |

PDF描述 |

|---|---|

| VI-J4L-MY-F2 | CONVERTER MOD DC/DC 28V 50W |

| FMS6501MSA28X | IC VIDEO SW MATRIX 12X9 28SSOP |

| VI-J4K-MY-F4 | CONVERTER MOD DC/DC 40V 50W |

| RP13A-12RA-13PA | CONN RECEPT 13POS MALE DIP |

| VI-J4K-MY-F3 | CONVERTER MOD DC/DC 40V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EL1881CSZ-T13 | 功能描述:视频 IC EL1881CSZ SYNC SEPERATOR RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| EL1881CSZ-T7 | 功能描述:视频 IC EL1881CSZ SYNC SEPERATOR RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| EL1881CSZ-T7A | 功能描述:视频 IC EL1881CSZ SYNC SEPERATOR RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| EL1882C | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Sync Separator w/50% Slice, AGC |

| EL1882CN | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Sync Separator w/50% Slice, AGC |

发布紧急采购,3分钟左右您将得到回复。