- 您现在的位置:买卖IC网 > PDF目录10587 > EL4583AISZ-T13 (Intersil)IC SYNC SEPARATOR S-H 50% 16SOIC PDF资料下载

参数资料

| 型号: | EL4583AISZ-T13 |

| 厂商: | Intersil |

| 文件页数: | 5/10页 |

| 文件大小: | 0K |

| 描述: | IC SYNC SEPARATOR S-H 50% 16SOIC |

| 标准包装: | 2,500 |

| 类型: | 同步分离器 |

| 应用: | 多媒体显示器,测试设备 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 16-SOIC |

| 包装: | 带卷 (TR) |

4

FN7503.2

November 12, 2010

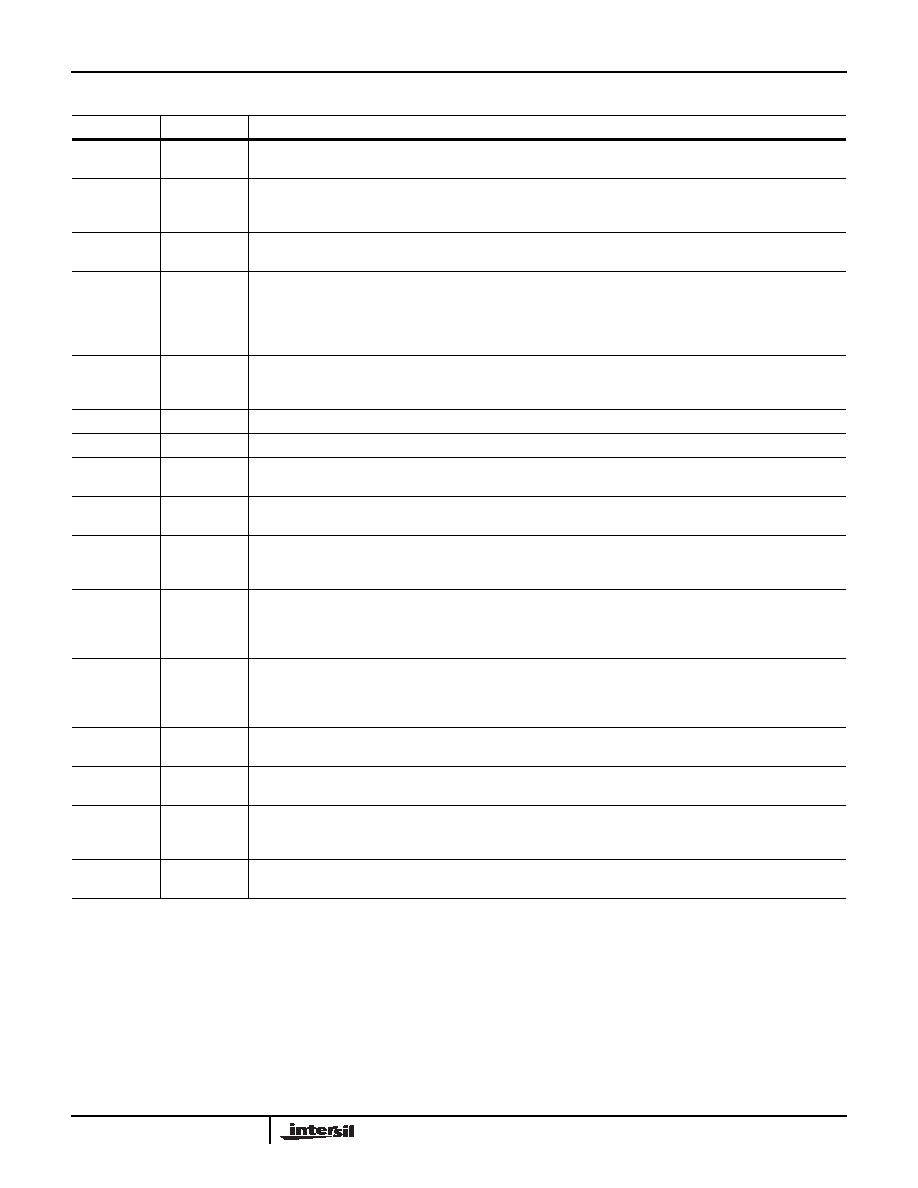

Pin Descriptions

PIN NUMBER

PIN NAME

PIN FUNCTION

1

Filter Cut-Off

A resistor RF connected between this input and ground determines the input filter characteristic. Increasing RF

increases the filter 3.58MHz color burst attenuation. See the typical performance characteristics.

2Set Detect

Level

A resistor RLV connected between pin 2 and ground determines the value of the minimum signal which triggers

the loss of signal output on pin 10. The relationship is VPMIN = 0.75RLV/RSET, where VPMIN is the minimum

detected sync pulse amplitude applied to pin 4. See the typical performance characteristics.

3Composite

Sync Output

This output replicates all the sync inputs on the input video.

4

Filter Input

The filter is a 3 pole active filter with a gain of 2, designed to produce a constant phase delay of nominally 260ns

with signal amplitude. Resistor RF on pin 1 controls the filter cut-off. An internal clamp sets the minimum voltage

on pin 4 at 1.55V when the input becomes low impedance. Above the clamp voltage, an input current of 1A

charges the input coupling capacitor. With loss of signal, the current source switches to a value of 10A, for faster

signal recovery.

5

Vertical Sync

Output

The vertical sync output is synchronous with the first serration pulse rising edge in the vertical interval of the input

signal and ends on the trailing edge of the first equalizing Output pulse after the vertical interval. It will therefore

be slightly more than 3H lines wide.

6

Digital Ground This is the ground return for digital buffer outputs.

7

Filter Output

Output of the active 3 pole filter which has its input on pin 4. It is recommended to ac couple the output to pin 8.

8

Video Input

This input can be directly driven by the signal if it is desired to bypass the filter, for example, in the case of strong

clean signals. This input is 6dB less sensitive than the filter input.

9

Level Output

This pin provides an analog voltage which is nominally equal to twice the sync pulse amplitude of the video input

signal applied to pin 4. It therefore provides an indication of signal strength.

10

No Signal

Detect Output

This is a digital output which goes high when either a) loss of input signal or b) the input signal level falls below

a predetermined amplitude as set by RLV on pin 2. There will be several horizontal lines delay before the output

is initiated.

11

Burst/Back

Porch Output

The start of back porch output is triggered on the trailing edge of normal H sync, and on the rising edge of

serration pulses in the vertical interval. The pulse is timed out internally to produce a one-shot output. The pulse

width is a function of RSET. This output can be used for d.c. restore functions where the back porch level is a

known reference.

12

RSET

The current through the resistor RSET determines the timing of the functions within the I.C. These functions

include the sampling of the sync pulse 50% point, back porch output and the 2H eliminator. For faster scan rates,

the resistor needs to be reduced inversely. For NTSC 15.7kHz scan rate RSET is 681k 1%. RSET must be a 1%

resistor.

13

Odd/Even

Output

Odd-even output is low for even field and high for odd field. The operation of this circuit has been improved for

rejecting spurious noise pulses such as those present in VCR signals.

14

VDD 5V

The internal circuits are designed to have a high immunity to supply variations, although as with most I.C.s a

0.1F decoupling capacitor is advisable.

15

Horizontal

Sync Output

This output produces only true H pulses of nominal width 5s. The leading edge is triggered from the leading

edge of the input H sync, with the same prop. delay as the composite sync The half line pulses present in the

input signal during vertical blanking are eliminated with an internal 2H eliminator circuit.

16

Analog

Ground

This is the ground return for the signal paths in the chips, RSET, RF and RLV.

EL4583A

相关PDF资料 |

PDF描述 |

|---|---|

| MS3106A14S-5S | CONN PLUG 5POS W/SOCKET SOLDER |

| SP232ACP-L | IC DVR/RCVR RS232 LP 16PDIP |

| EL1883ISZ-T7A | IC VID SYNC SEPARATOR HORZ 8SOIC |

| 97-3106A-14S-2P | CONN PLUG 4POS W/PINS |

| VE-J0F-MY-F4 | CONVERTER MOD DC/DC 72V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EL4583AISZ-T7 | 功能描述:视频 IC EL4583AISZ SYNC SEP 50% SLICE S-H FLTR H RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| EL4583AISZ-T7S2716 | 制造商:Intersil Corporation 功能描述: |

| EL4583C | 制造商:ELANTEC 制造商全称:ELANTEC 功能描述:Sync Separator, 50% Slice, S-H, Filter, HOUT |

| EL4583CN | 功能描述:IC VIDEO SYNC SEPARATOR 16-DIP RoHS:否 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 产品变化通告:Product Discontinuation 07/Mar/2011 标准包装:3,000 系列:OMNITUNE™ 类型:调谐器 应用:移动电话,手机,视频显示器 安装类型:表面贴装 封装/外壳:65-WFBGA 供应商设备封装:PG-WFSGA-65 包装:带卷 (TR) 其它名称:SP000365064 |

| EL4583CS | 功能描述:IC VIDEO SYNC SEPARATOR 16-SOIC RoHS:否 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 产品变化通告:Product Discontinuation 07/Mar/2011 标准包装:3,000 系列:OMNITUNE™ 类型:调谐器 应用:移动电话,手机,视频显示器 安装类型:表面贴装 封装/外壳:65-WFBGA 供应商设备封装:PG-WFSGA-65 包装:带卷 (TR) 其它名称:SP000365064 |

发布紧急采购,3分钟左右您将得到回复。