- 您现在的位置:买卖IC网 > PDF目录16333 > EL4584CSZ-EVAL (Intersil)EVALUATION BOARD FOR EL4584 PDF资料下载

参数资料

| 型号: | EL4584CSZ-EVAL |

| 厂商: | Intersil |

| 文件页数: | 1/15页 |

| 文件大小: | 0K |

| 描述: | EVALUATION BOARD FOR EL4584 |

| 标准包装: | 1 |

| 主要目的: | 计时,PLL |

| 嵌入式: | 否 |

| 已用 IC / 零件: | EL4584CSZ |

| 主要属性: | 适用于高达 36 MHz 的视频 |

| 次要属性: | 5V 电源,< 2ns 抖动(VCXO) |

| 已供物品: | 板 |

1

FN7174.3

EL4584

Horizontal Genlock, 4FSC

The EL4584 is a PLL (Phase Lock Loop) sub system,

designed for video applications but also suitable for general

purpose use up to 36MHz. In video applications, this device

generates a TTL/CMOS compatible Pixel Clock (CLK OUT)

which is a multiple of the TV horizontal scan rate and phase

locked to it.

The reference signal is a horizontal sync signal, TTL/CMOS

format, which can be easily derived from an analog

composite video signal with the EL4583 Sync Separator. An

input signal to “coast” is provided for applications where

periodic disturbances are present in the reference video

timing, such as VTR head switching. The Lock detector

output indicates correct lock.

The divider ratio is four ratios for NTSC and four similar

ratios for the PAL video timing standards, by external

selection of three control pins. These four ratios have been

selected for common video applications including 4FSC,

3FSC, 13.5MHz (CCIR 601 format) and square picture

elements used in some workstation graphics. To generate

8FSC, 6FSC, 27MHz (CCIR 601 format) etc. use the

EL4585, which includes an additional divide-by-two stage.

For applications where these frequencies are inappropriate

or for general purpose PLL applications, the internal divider

can be bypassed and an external divider chain used.

Features

36MHz, general purpose PLL

4FSC based timing (use the EL4585 for 8FSC)

Compatible with EL4583 sync separator

VCXO, Xtal, or LC tank oscillator

< 2ns jitter (VCXO)

User controlled PLL capture and lock

Compatible with NTSC and PAL TV formats

8 pre-programmed TV scan rate clock divisors

Selectable external divide for custom ratios

Single 5V, low current operation

Pb-Free available (RoHS compliant)

Applications

Pixel clock regeneration

Video compression engine (MPEG) clock generator

Video capture or digitization

PIP (Picture-in-Picture) timing generator

Text or graphics overlay timing

Demo Board

A demo PCB is available for this product.

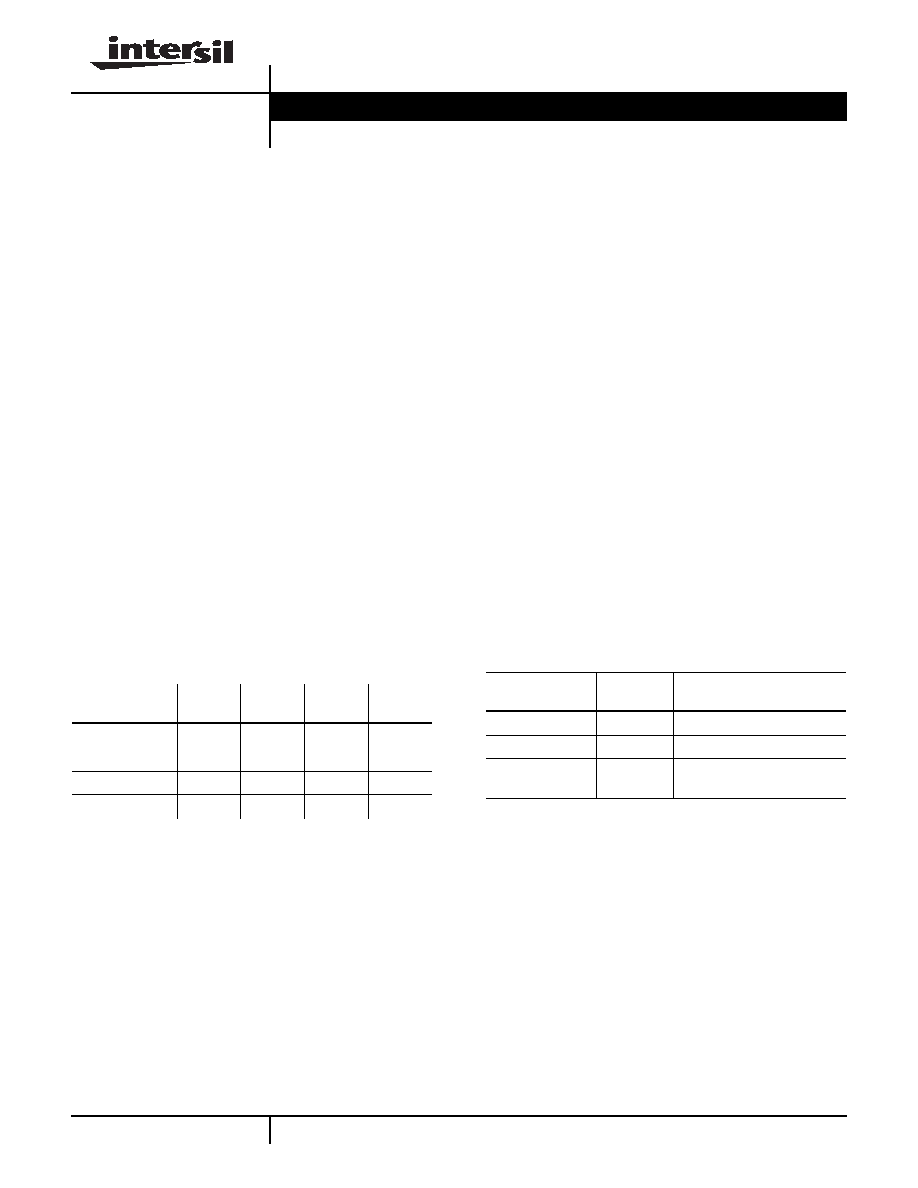

TABLE 1. FREQUENCIES AND DIVISORS

FUNCTION

3FSC

(Note 1)

CCIR 601

(Note 2)

SQUARE

(Note 3)

4FSC

Divisor

851

864

944

1135

PAL FOSC (MHz)

13.301

13.5

14.75

17.734

Divisor

682

858

780

910

NTSC FOSC (MHz)

10.738

13.5

12.273

14.318

NOTES:

1. 3FSC numbers do not yield integer divisors.

2. CCIR 601 Divisors yield 720 pixels in the portion of each line for

NTSC and PAL.

3. Square pixels format gives 640 pixels for NTSC and 768 pixels

for PAL in the active portion.

Ordering Information

PART NUMBER

PART

MARKING

PACKAGE

PKG.

DWG. #

EL4584CN

16 Ld PDIP MDP0031

EL4584CS*

EL4584CS

16 Ld SOIC MDP0027

EL4584CSZ*

(Note)

EL4584CSZ

16 Ld SOIC

(Pb-free)

MDP0027

**For 6FSC and 8FSC clock frequencies, see EL4585 datasheet.

NOTE: These Intersil Pb-free plastic packaged products employ

special Pb-free material sets; molding compounds/die attach

materials and 100% matte tin plate PLUS ANNEAL - e3 termination

finish, which is RoHS compliant and compatible with both SnPb and

Pb-free soldering operations. Intersil Pb-free products are MSL

classified at Pb-free peak reflow temperatures that meet or exceed

the Pb-free requirements of IPC/JEDEC J STD-020.

Data Sheet

May 9, 2008

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright Intersil Americas Inc. 2003-2008. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

相关PDF资料 |

PDF描述 |

|---|---|

| M3CCK-1640K | IDC CABLE - MKC16K/MC16F/MKC16K |

| ILSB0805ER270K | INDUCTOR 27UH 10% 0805 |

| RYM12DTAH-S189 | CONN EDGECARD 24POS R/A .156 SLD |

| 2-6278901-0 | C/A 62.5/125UM,ZIPST,MTRJ 20M |

| BRC2518T1R5M | INDUCTOR 1.5UH 1.3A 1007 SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EL4584CSZ-T13 | 功能描述:锁相环 - PLL EL4584CSZ H-SYNC GEN LOCK RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| EL4584CSZ-T7 | 功能描述:锁相环 - PLL EL4584CSZ H-SYNC GEN LOCK RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| EL4585 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Horizontal Genlock, 8FSC |

| EL4585C | 制造商:ELANTEC 制造商全称:ELANTEC 功能描述:Horizontal Genlock, 8 FSC |

| EL4585CN | 功能描述:IC PLL VIDEO GP 36MHZ 16-DIP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。