- 您现在的位置:买卖IC网 > PDF目录10669 > EL9112ILZ (Intersil)IC RCVR/EQLZR DIFF 150MHZ 28-QFN PDF资料下载

参数资料

| 型号: | EL9112ILZ |

| 厂商: | Intersil |

| 文件页数: | 3/13页 |

| 文件大小: | 0K |

| 描述: | IC RCVR/EQLZR DIFF 150MHZ 28-QFN |

| 标准包装: | 90 |

| 类型: | 接收器 |

| 驱动器/接收器数: | 0/3 |

| 规程: | 双绞线 |

| 电源电压: | 5V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-VFQFN 裸露焊盘 |

| 供应商设备封装: | * |

| 包装: | 管件 |

| 产品目录页面: | 1239 (CN2011-ZH PDF) |

11

FN7450.4

May 9, 2007

Decoding is based on the EL4543 encoding scheme, as

level system, which has been designed such that the sum of

the common mode voltages results in a fixed average DC

level with no AC content. This eliminates the effect of EMI

radiation into the common mode signals along the twisted

pairs of the cable.

The common mode voltages are initially extracted by the

EL9111 from the three input pairs. These are then passed to

an internal logic decoding block to provide Horizontal and

Vertical sync output signals (HOUT and VOUT).

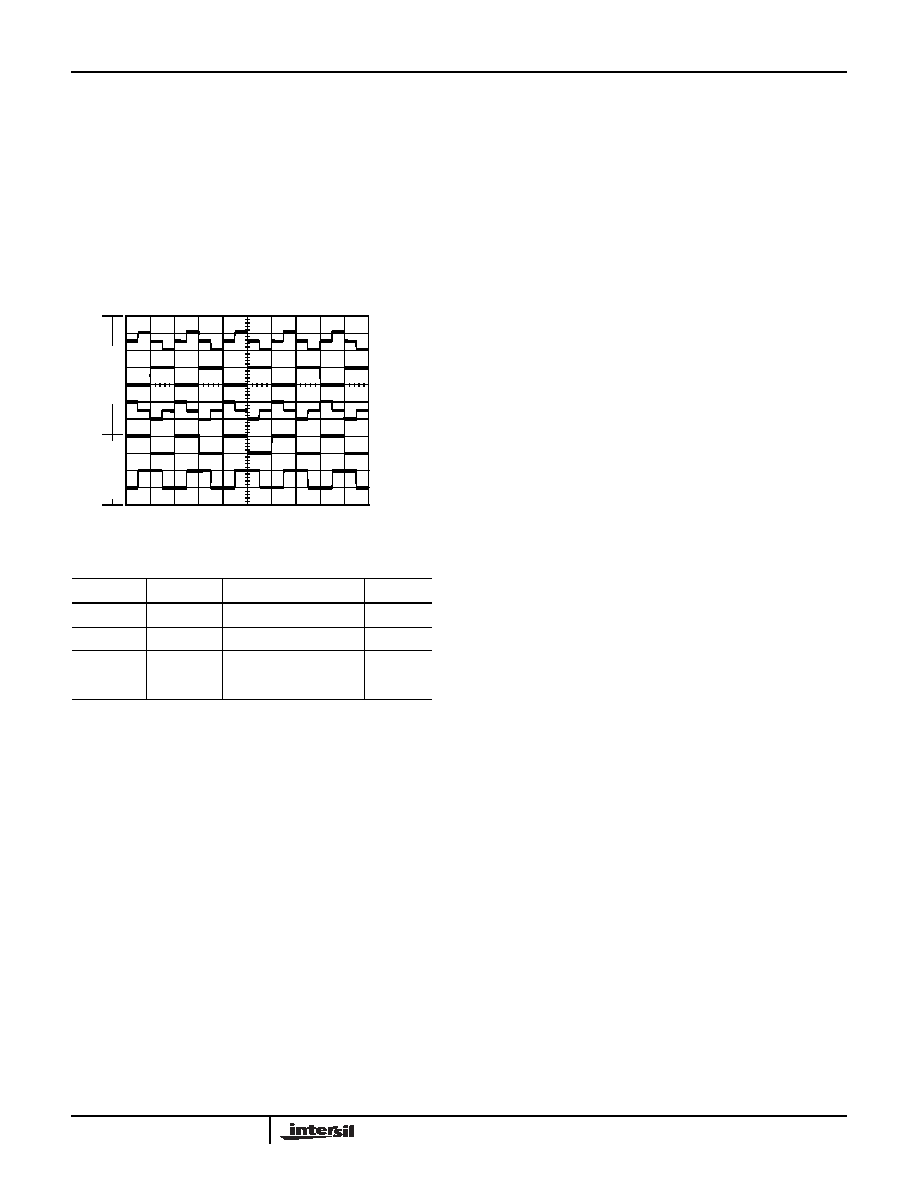

FIGURE 27. H AND V SYNCS ENCODED

Sync Ref

The Sync Ref pin is the reference level for the logic low of the

sync outputs. It can be tied to 0V or -5V, but for typical

operation, the Sync Ref pin would tie to 0V. The Sync output

logic low level approaches Sync Ref within VCESAT; the logic

high will approach VSP within VCESAT. The EL9111 operating

with a 10V single supply and Sync Ref at ground will cause the

HOUT and VOUT pins to go from ground to VSP, a 10V swing.

This is too large a voltage for logic inputs, so an output voltage

divider of 1k

Ω series from the outputs with 1kΩ to ground will

reduce the output logic levels to 0V and 5V. Different logic

levels may require different output divider ratios.

The Sync Ref is intended to sink all the switching currents as

transitions to logic low are made. This prevents switching

signals crosstalk to the main chip 0V line, as well as adding the

flexibility of referencing to -5V. Thus, the logic output buffer

does use Sync Ref as its negative supply. The Sync Ref pin is

connected to the analog -5V or analog ground as needed and

is a separate pin to prevent noise coupling in the chip.

EL9111 with Single Ended Coax Input

The EL9111 is designed to use twisted pair cat 5 cable input

with sync encoded as differential CMV on the RGB pairs.

Coax cable inputs may be used with a few changes and

limitations. Coax cable cannot have sync encoded as CMV,

so the coax shields are grounded along with the EL9111

RGB minus inputs. The coax center conductor is terminated

with 75

Ω and connected to the RGB plus inputs. The result

is half the video signal will be seen as CMV by the sync

decoding circuit that decodes the video as sync. This causes

noise on the RGB outputs. The noise may be eliminated by

connecting the Sync Ref pin to VSP to disable the Sync

Outputs which now typically go to about 3V with +5VSP.

TABLE 1. H AND V SYNC DECODING

RED CM

GREEN CM

BLUE CM

HSYNC

VSYNC

Mid

High

Low

High

Low

Mid

Low

High

Low

High

Mid

High

Low

Mid

Low

High

NOTE: Level ‘Mid’ is halfway between ‘High’ and ‘Low’

TIME (0.5ms/DIV)

VOLTA

GE

(0.

5

V/

DIV

)

BLUE CM

OUT (CH A)

GREEN CM

OUT (CH B)

RED CM

OUT (CH C)

VSYNC

HSYNC

VO

LTA

GE

(2.

5

V/

DIV

)

EL9111, EL9112

相关PDF资料 |

PDF描述 |

|---|---|

| VE-J7P-MY-F1 | CONVERTER MOD DC/DC 13.8V 50W |

| CS5364-DQZ | IC ADC 4CH 114DB 216KHZ 48-LQFP |

| VE-J7N-MY-F3 | CONVERTER MOD DC/DC 18.5V 50W |

| AD7859ASZ | IC ADC 12BIT 8CH LP 44-MQFP |

| VE-J7N-MY-F2 | CONVERTER MOD DC/DC 18.5V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EL9112ILZ-T13 | 功能描述:总线接收器 EL9112ILZ TRPL DIFFR NTLCVR/EQUALIZER RoHS:否 制造商:Texas Instruments 接收机数量:4 接收机信号类型:Differential 接口类型:EIA/TIA-422-B, V.11 工作电源电压:3.3 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:TSSOP-16 封装:Reel |

| EL9112ILZ-T7 | 功能描述:总线接收器 EL9112ILZ TRPL DIFFR NTLCVR/EQUALIZER RoHS:否 制造商:Texas Instruments 接收机数量:4 接收机信号类型:Differential 接口类型:EIA/TIA-422-B, V.11 工作电源电压:3.3 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:TSSOP-16 封装:Reel |

| EL9115 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple Analog Video Delay Line |

| EL9115_06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple Analog Video Delay Line |

| EL9115_08 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple Analog Video Delay Line |

发布紧急采购,3分钟左右您将得到回复。