- 您现在的位置:买卖IC网 > PDF目录299030 > EP20K100BC196-1 (ALTERA CORP) LOADABLE PLD, PBGA196 PDF资料下载

参数资料

| 型号: | EP20K100BC196-1 |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, PBGA196 |

| 文件页数: | 33/68页 |

| 文件大小: | 975K |

| 代理商: | EP20K100BC196-1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页当前第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

39

4317K–AVR–03/2013

AT90PWM2/3/2B/3B

When switching between prescaler settings, the System Clock Prescaler ensures that no

glitches occurs in the clock system. It also ensures that no intermediate frequency is higher than

neither the clock frequency corresponding to the previous setting, nor the clock frequency corre-

sponding to the new setting. The ripple counter that implements the prescaler runs at the

frequency of the undivided clock, which may be faster than the CPU's clock frequency. Hence, it

is not possible to determine the state of the prescaler - even if it were readable, and the exact

time it takes to switch from one clock division to the other cannot be exactly predicted. From the

time the CLKPS values are written, it takes between T1 + T2 and T1 + 2 * T2 before the new

clock frequency is active. In this interval, 2 active clock edges are produced. Here, T1 is the pre-

vious clock period, and T2 is the period corresponding to the new prescaler setting.

To avoid unintentional changes of clock frequency, a special write procedure must be followed

to change the CLKPS bits:

1.

Write the Clock Prescaler Change Enable (CLKPCE) bit to one and all other bits in

CLKPR to zero.

2.

Within four cycles, write the desired value to CLKPS while writing a zero to CLKPCE.

Interrupts must be disabled when changing prescaler setting to make sure the write procedure is

not interrupted.

7.10.1

Clock Prescaler Register – CLKPR

Bit 7 – CLKPCE: Clock Prescaler Change Enable

The CLKPCE bit must be written to logic one to enable change of the CLKPS bits. The CLKPCE

bit is only updated when the other bits in CLKPR are simultaniosly written to zero. CLKPCE is

cleared by hardware four cycles after it is written or when CLKPS bits are written. Rewriting the

CLKPCE bit within this time-out period does neither extend the time-out period, nor clear the

CLKPCE bit.

Bits 3..0 – CLKPS3..0: Clock Prescaler Select Bits 3 - 0

These bits define the division factor between the selected clock source and the internal system

clock. These bits can be written run-time to vary the clock frequency to suit the application

requirements. As the divider divides the master clock input to the MCU, the speed of all synchro-

nous peripherals is reduced when a division factor is used. The division factors are given in

The CKDIV8 Fuse determines the initial value of the CLKPS bits. If CKDIV8 is unprogrammed,

the CLKPS bits will be reset to “0000”. If CKDIV8 is programmed, CLKPS bits are reset to

“0011”, giving a division factor of 8 at start up. This feature should be used if the selected clock

source has a higher frequency than the maximum frequency of the device at the present operat-

ing conditions. Note that any value can be written to the CLKPS bits regardless of the CKDIV8

Fuse setting. The Application software must ensure that a sufficient division factor is chosen if

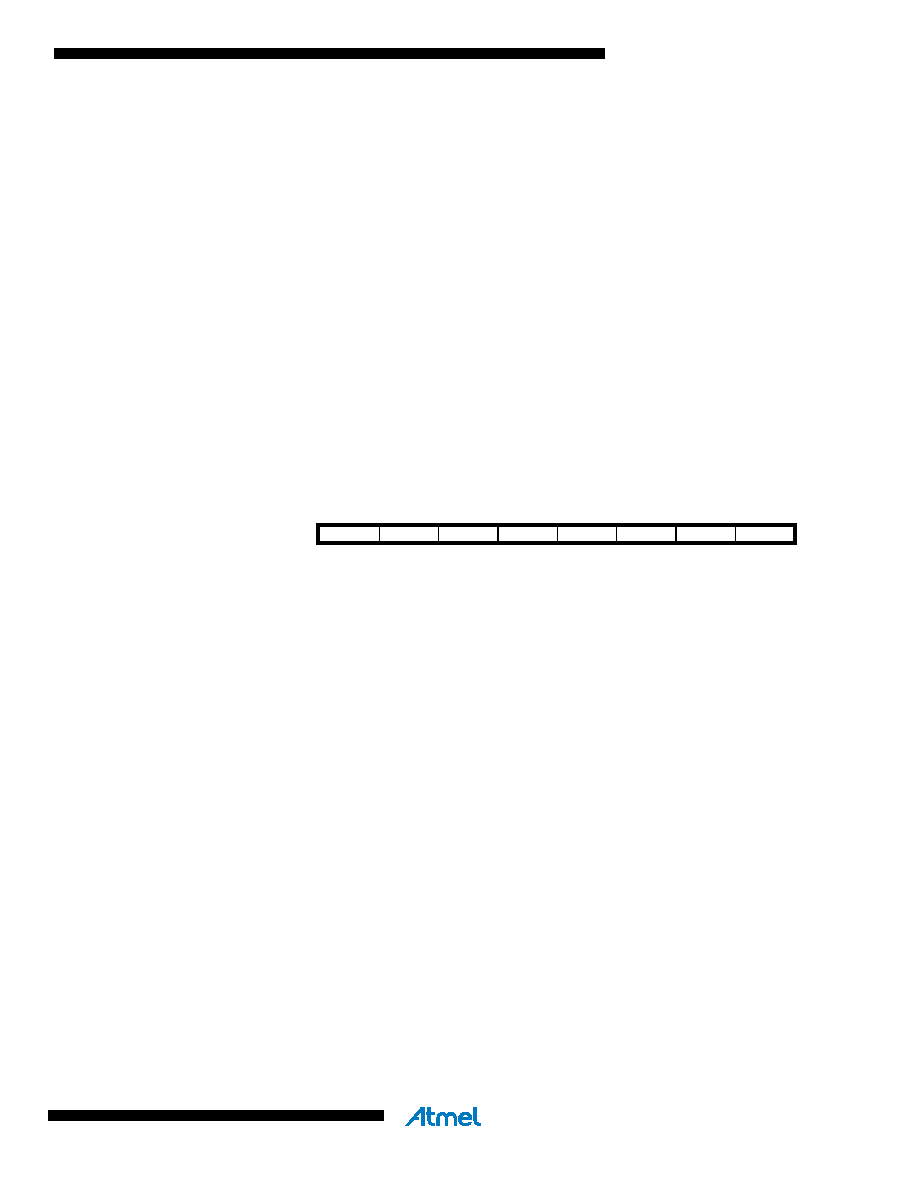

Bit

7

654

3

2

1

0

CLKPCE

–

CLKPS3

CLKPS2

CLKPS1

CLKPS0

CLKPR

Read/Write

R/W

R

R/W

Initial Value

0

See Bit Description

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K100BC196-2 | LOADABLE PLD, PBGA196 |

| EP20K100BC196-3 | LOADABLE PLD, PBGA196 |

| EP20K100BI196-1 | LOADABLE PLD, PBGA196 |

| EP20K100BI196-2 | LOADABLE PLD, PBGA196 |

| EP20K100BI196-3 | LOADABLE PLD, PBGA196 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K100BC356-1 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 252 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100BC356-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100BC356-1V | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP20K100BC356-2 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 252 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100BC356-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

发布紧急采购,3分钟左右您将得到回复。