- 您现在的位置:买卖IC网 > PDF目录97924 > EP20K200QC208-1ES FPGA PDF资料下载

参数资料

| 型号: | EP20K200QC208-1ES |

| 英文描述: | FPGA |

| 中文描述: | FPGA的 |

| 文件页数: | 64/114页 |

| 文件大小: | 1623K |

| 代理商: | EP20K200QC208-1ES |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页当前第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页

Altera Corporation

53

APEX 20K Programmable Logic Device Family Data Sheet

for APEX 20KE devices.

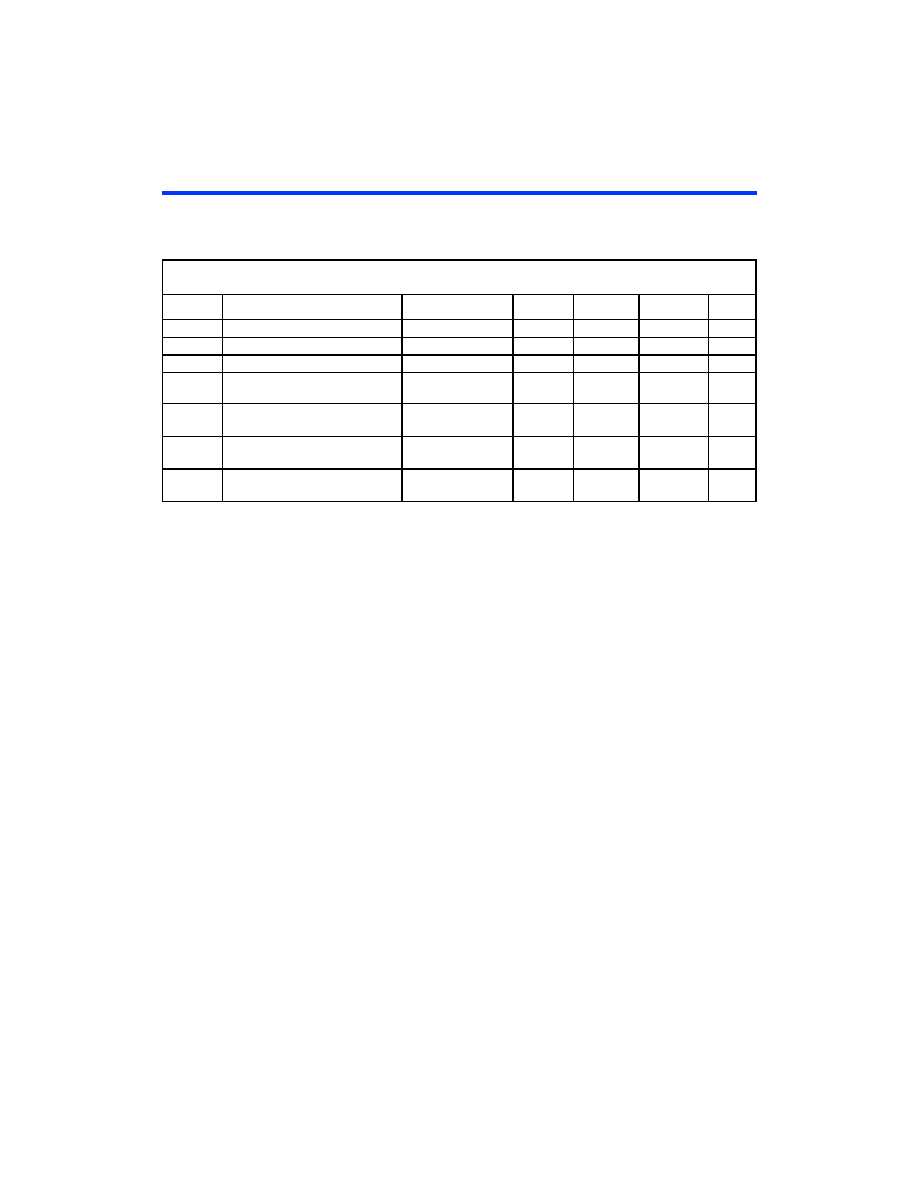

Table 17. APEX 20KE ClockLock & ClockBoost Parameters

Symbol

Parameter

Condition

Min

Typ

Max

Unit

tR

Input rise time

5ns

tF

Input fall time

5ns

tINDUTY

Input duty cycle

40

60

%

tINJITTER

Input jitter peak-to-peak

2

% of input

period

peak-to-

peak

tOUTJITTER Jitter on ClockLock or ClockBoost-

generated clock

0.35

% of

output period

RMS

tOUTDUTY

Duty cycle for ClockLock or

ClockBoost-generated clock

45

55

%

tLOCK (2),

Time required for ClockLock or

ClockBoost to acquire lock

40

s

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K200QC208-2 | Field Programmable Gate Array (FPGA) |

| EP20K200QC208-2ES | FPGA |

| EP20K200QC208-3 | Field Programmable Gate Array (FPGA) |

| EP20K200RC240-1 | Field Programmable Gate Array (FPGA) |

| EP20K200RC240-1ES | FPGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K200QC208-2 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| EP20K200QC208-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K200QC208-3 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| EP20K200QC208-3ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K200QC240-1 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

发布紧急采购,3分钟左右您将得到回复。