- 您现在的位置:买卖IC网 > PDF目录362744 > EPC1441 (Altera Corporation) Configuration Devices for ACEX, APEX, FLEX & Mercury Devices PDF资料下载

参数资料

| 型号: | EPC1441 |

| 厂商: | Altera Corporation |

| 英文描述: | Configuration Devices for ACEX, APEX, FLEX & Mercury Devices |

| 中文描述: | 配置器件ACEX,顶点,柔性 |

| 文件页数: | 9/28页 |

| 文件大小: | 380K |

| 代理商: | EPC1441 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

Altera Corporation

9

Configuration Devices for ACEX, APEX, FLEX & Mercury Devices Data Sheet

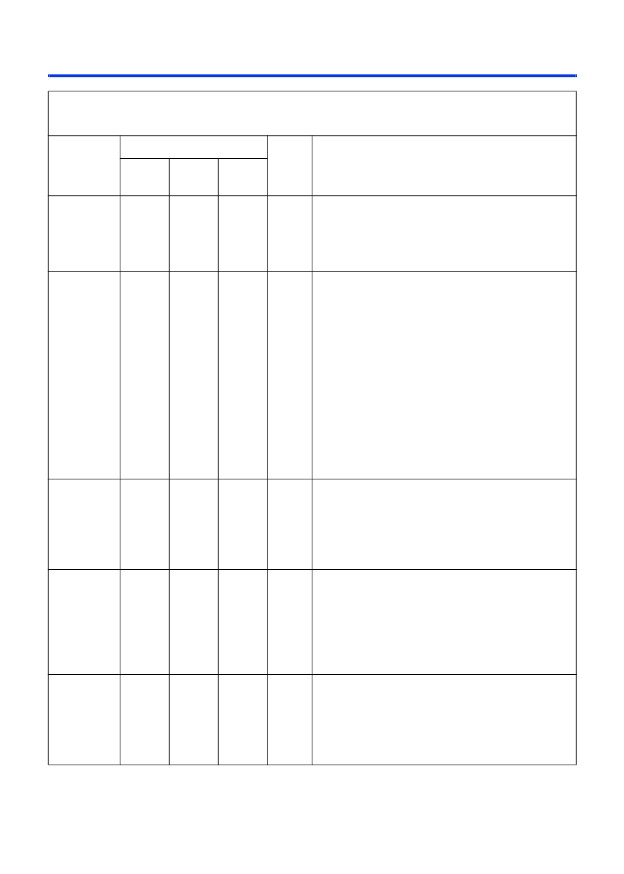

Table 4. EPC2, EPC1, & EPC1441 Pin Functions During ACEX 1K, APEX 20K, FLEX 10K, FLEX 6000 &

Mercury Configuration (Part 1 of 2)

Pin Name

Pin Number

Pin

Type

Description

8-Pin

PDIP

(1)

20-Pin

PLCC

32-Pin

TQFP

(2)

DATA

1

2

31

Output

Serial data output. The

DATA

pin is tri-stated before

configuration when the

nCS

pin is high, and after the

configuration device finishes sending its configuration

data. This operation is independent of the device

’

s

position in the cascade chain.

DCLK

is a clock output when configuring with a single

configuration device or when the configuration device is

the first device in a configuration device chain.

DCLK

is

a clock input for subsequent configuration devices in a

configuration device chain. Rising edges on

DCLK

increment the internal address counter and present the

next bit of data to the

DATA

pin. The counter is

incremented only if the

OE

input is held high, the

nCS

input is held low, and all configuration data has not

been transferred to the target device. When configuring

with the first EPC2 or EPC1 device in a configuration

device chain or with a single EPC1441 device, the

DCLK

pin drives low after configuration is complete or

when

OE

is low.

Output enable (active high) and reset (active low). A

low logic level resets the address counter. A high logic

level enables

DATA

and permits the address counter to

count. If this pin is low (reset) during configuration, the

internal oscillator becomes inactive and

DCLK

drives

low. See

“

Error Detection Circuitry

”

on

page 17

.

Chip select input (active low). A low input allows

DCLK

to increment the address counter and enables

DATA

to

drive out. If the EPC1 or EPC2 is reset with

nCS

low, the

device initializes as the first device in a configuration

chain. If the EPC1 or EPC2 device is reset with

nCS

high, the device initializes as the subsequent device in

the chain.

Cascade select output (active low). This output goes

low when the address counter has reached its

maximum value. In a chain of EPC1 or EPC2 devices,

the

nCASC

pin of one device is connected to the

nCS

pin

of the next device, which permits

DCLK

to clock data

from the next EPC1 or EPC2 device in the chain.

DCLK

2

4

2

I/O

OE

(3)

3

8

7

Open-

Drain

I/O

nCS

(3)

4

9

10

Input

nCASC

(4)

6

12

15

Output

相关PDF资料 |

PDF描述 |

|---|---|

| EPC4xxx | 2. Enhanced Configuration Devices (EPC4, EPC8 & EPC16) Data Sheet |

| EPC16QC100 | 2. Enhanced Configuration Devices (EPC4, EPC8 & EPC16) Data Sheet |

| EPC16QI100 | 2. Enhanced Configuration Devices (EPC4, EPC8 & EPC16) Data Sheet |

| EPC8xxx | 2. Enhanced Configuration Devices (EPC4, EPC8 & EPC16) Data Sheet |

| EPC8QC100 | 2. Enhanced Configuration Devices (EPC4, EPC8 & EPC16) Data Sheet |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EPC1441LC20 | 功能描述:FPGA-配置存储器 IC - Ser. Config Mem Flash 440Kb 8 MHz RoHS:否 制造商:Altera Corporation 存储类型:Flash 存储容量:1.6 Mbit 工作频率:10 MHz 电源电压-最大:5.25 V 电源电压-最小:3 V 电源电流:50 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:PLCC-20 |

| EPC1441LC20N | 功能描述:FPGA-配置存储器 IC - Ser. Config Mem Flash 440Kb 8 MHz RoHS:否 制造商:Altera Corporation 存储类型:Flash 存储容量:1.6 Mbit 工作频率:10 MHz 电源电压-最大:5.25 V 电源电压-最小:3 V 电源电流:50 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:PLCC-20 |

| EPC1441LI20 | 功能描述:FPGA-配置存储器 IC - Ser. Config Mem Flash 440Kb 8 MHz RoHS:否 制造商:Altera Corporation 存储类型:Flash 存储容量:1.6 Mbit 工作频率:10 MHz 电源电压-最大:5.25 V 电源电压-最小:3 V 电源电流:50 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:PLCC-20 |

| EPC1441LI20N | 功能描述:FPGA-配置存储器 IC - Ser. Config Mem Flash 440Kb 8 MHz RoHS:否 制造商:Altera Corporation 存储类型:Flash 存储容量:1.6 Mbit 工作频率:10 MHz 电源电压-最大:5.25 V 电源电压-最小:3 V 电源电流:50 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:PLCC-20 |

| EPC1441PC8 | 功能描述:FPGA-配置存储器 IC - Ser. Config Mem Flash 440Kb 8 MHz RoHS:否 制造商:Altera Corporation 存储类型:Flash 存储容量:1.6 Mbit 工作频率:10 MHz 电源电压-最大:5.25 V 电源电压-最小:3 V 电源电流:50 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:PLCC-20 |

发布紧急采购,3分钟左右您将得到回复。