- 您现在的位置:买卖IC网 > PDF目录19911 > EPC1PI8N (Altera)IC CONFIG DEVICE 1MBIT 8-DIP PDF资料下载

参数资料

| 型号: | EPC1PI8N |

| 厂商: | Altera |

| 文件页数: | 6/26页 |

| 文件大小: | 0K |

| 描述: | IC CONFIG DEVICE 1MBIT 8-DIP |

| 产品培训模块: | Three Reasons to Use FPGA's in Industrial Designs |

| 标准包装: | 100 |

| 系列: | EPC |

| 可编程类型: | OTP |

| 存储容量: | 1Mb |

| 电源电压: | 3 V ~ 3.6 V,4.5 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-DIP(0.300",7.62mm) |

| 供应商设备封装: | 8-PDIP |

| 包装: | 管件 |

| 产品目录页面: | 604 (CN2011-ZH PDF) |

| 配用: | PLMJ1213-ND - PROGRAMMER ADAPTER 20 PIN J-LEAD |

| 其它名称: | 544-1375-5 EPC1PI8N-ND |

Page 14

IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing

Configuration Devices for SRAM-Based LUT Devices

January 2012

Altera Corporation

IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing

The EPC2 device provides JTAG BST circuitry that complies with the IEEE Std.

1149.1-1990 specification. You can perform JTAG BST before or after configuration, but

not during configuration. Table 6 lists the JTAG instructions supported by the EPC2

device.

f For more information, refer to AN39: IEEE 1149.1 JTAG Boundary-Scan Testing in Altera

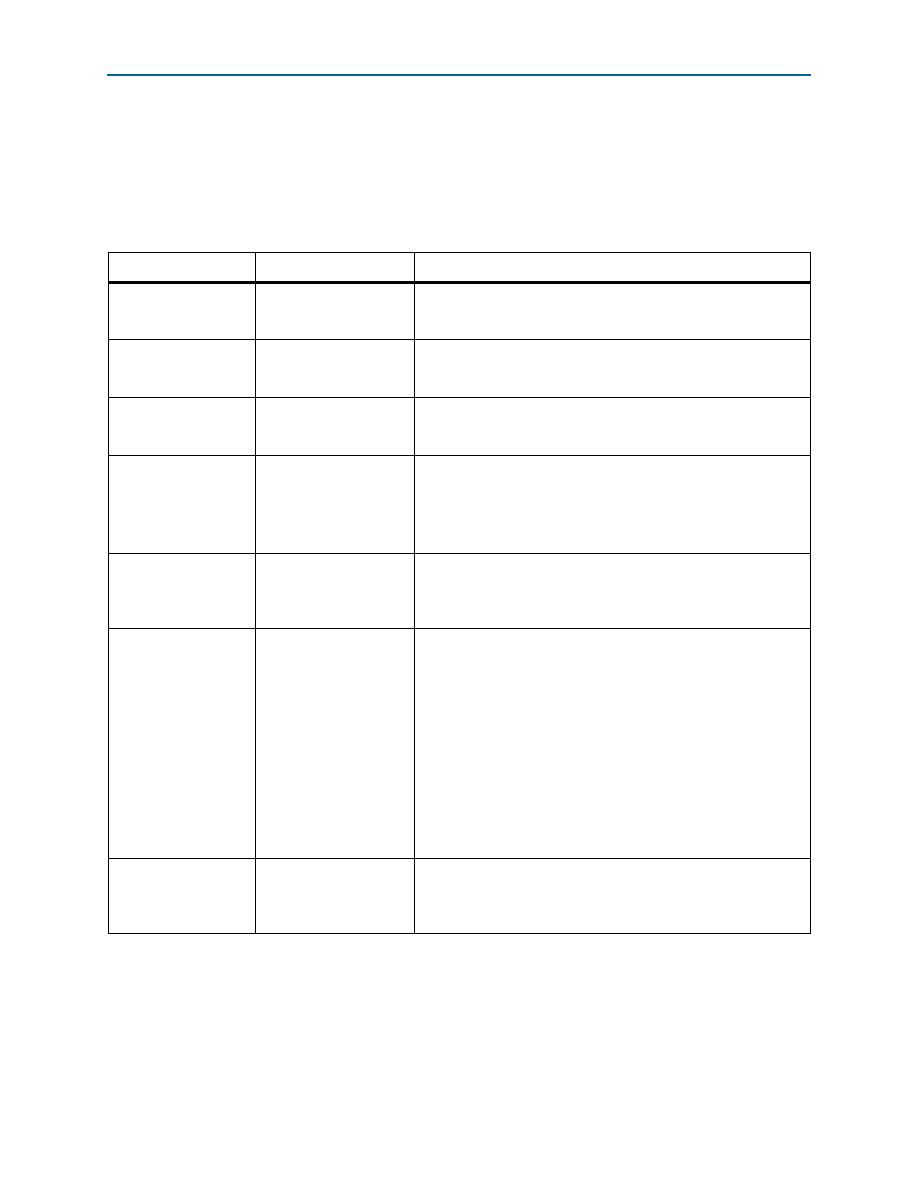

Table 6. EPC2 Device JTAG Instructions

JTAG Instruction

OPCODE

Description

SAMPLE/PRELOAD

00 0101 0101

Allows a snapshot of a signal at the device pins to be captured and

examined during normal device operation and permits an initial data

pattern output at the device pins.

EXTEST

00 0000 0000

Allows the external circuitry and board-level interconnections to be

tested by forcing a test pattern at the output pins and capturing

results at the input pins.

BYPASS

11 1111 1111

Places the 1-bit bypass register between the TDI and TDO pins,

which allows the BST data to pass synchronously through a selected

device to adjacent devices during normal device operation.

IDCODE

00 0101 1001

Selects the device IDCODE register and places it between the TDI

and TDO pins, allowing the device IDCODE to be serially shifted out of

the TDO pin. The device IDCODE for the EPC2 configuration device is

shown below:

0000 0001000000000010 00001101110 1

USERCODE

00 0111 1001

Selects the USERCODE register and places it between the TDI and

TDO

pins, allowing the USERCODE to be serially shifted out of the

TDO

pin. The 32-bit USERCODE is a programmable user-defined

pattern.

INIT_CONF

00 0110 0001

Initiates the FPGA re-configuration process by pulsing the

nINIT_CONF

pin low, which is connected to the FPGAs nCONFIG

pins. After this instruction is updated, the nINIT_CONF pin is pulsed

low when the JTAG state machine enters the Run-Test/Idle state. The

nINIT_CONF

pin is then released and nCONFIG is pulled high by the

resistor after the JTAG state machine goes out of Run-Test/Idle state.

The FPGA configuration starts after the nCONFIG pin goes high. As a

result, the FPGA is configured with the new configuration data stored

in the configuration device. You can add this function to your

programming file (.pof, .jam, .jbc) in the Quartus II software by

enabling the Initiate configuration after programming option in the

Programmer options window (Options menu). This instruction is

also used by the MAX+PLUS II software, .jam files, and .jbc files.

ISP Instructions

—

These instructions are used when programming an EPC2 device

using JTAG ports with a USB-Blaster, MasterBlaster, ByteBlaster II,

EthernetBlaster, or ByteBlasterMV download cable, or using a .jam,

.jbc, or .svf file using an embedded processor.

相关PDF资料 |

PDF描述 |

|---|---|

| GMC43DRTH-S93 | CONN EDGECARD 86POS DIP .100 SLD |

| EBM15DCBS | CONN EDGECARD 30POS R/A .156 SLD |

| XC17S15AVO8C | IC PROM SER 5K 8-SOIC |

| T86E227M010EBAS | CAP TANT 220UF 10V 20% 2917 |

| TAJE337M010RNJ | CAP TANT 330UF 10V 20% 2917 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EPC1VLC20 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Configuration EPROM |

| EPC1VLI20 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Configuration EPROM |

| EPC1VPC8 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Configuration EPROM |

| EPC1VPI8 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Configuration EPROM |

| EPC2 | 制造商:ALTERA 制造商全称:Altera Corporation 功能描述:SRAM-Based LUT Devices |

发布紧急采购,3分钟左右您将得到回复。