参数资料

| 型号: | EPF6016ATC144-1N |

| 厂商: | Altera |

| 文件页数: | 46/52页 |

| 文件大小: | 0K |

| 描述: | IC FLEX 6000 FPGA 16K 144-TQFP |

| 产品培训模块: | Three Reasons to Use FPGA's in Industrial Designs |

| 标准包装: | 180 |

| 系列: | FLEX 6000 |

| LAB/CLB数: | 132 |

| 逻辑元件/单元数: | 1320 |

| 输入/输出数: | 117 |

| 门数: | 16000 |

| 电源电压: | 3 V ~ 3.6 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-TQFP(20x20) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页当前第46页第47页第48页第49页第50页第51页第52页

50

Altera Corporation

FLEX 6000 Programmable Logic Device Family Data Sheet

Operating Modes

The FLEX 6000 architecture uses SRAM configuration elements that

require configuration data to be loaded every time the circuit powers

up. This process of physically loading the SRAM data into a FLEX

6000 device is known as configuration. During initialization—a

process that occurs immediately after configuration—the device

resets registers, enables I/O pins, and begins to operate as a logic

device. The I/O pins are tri-stated during power-up, and before and

during configuration. The configuration and initialization processes

of a device are referred to as command mode; normal device operation

is called user mode.

SRAM configuration elements allow FLEX 6000 devices to be

reconfigured in-circuit by loading new configuration data into the

device. Real-time reconfiguration is performed by forcing the device

into command mode with a device pin, loading different

configuration data, reinitializing the device, and resuming user-

mode operation. The entire reconfiguration process requires less

than 100 ms and is used to dynamically reconfigure an entire system.

Also, in-field system upgrades can be performed by distributing new

configuration files.

Configuration Schemes

The configuration data for a FLEX 6000 device can be loaded with

one of three configuration schemes, which is chosen on the basis of

the target application. An EPC1 or EPC1441 configuration device or

intelligent controller can be used to control the configuration of a

FLEX 6000 device, allowing automatic configuration on system

power-up.

Multiple FLEX 6000 devices can be configured in any of the three

configuration schemes by connecting the configuration enable input

(nCE) and configuration enable output (nCEO) pins on each device.

Table 40 shows the data sources for each configuration scheme.

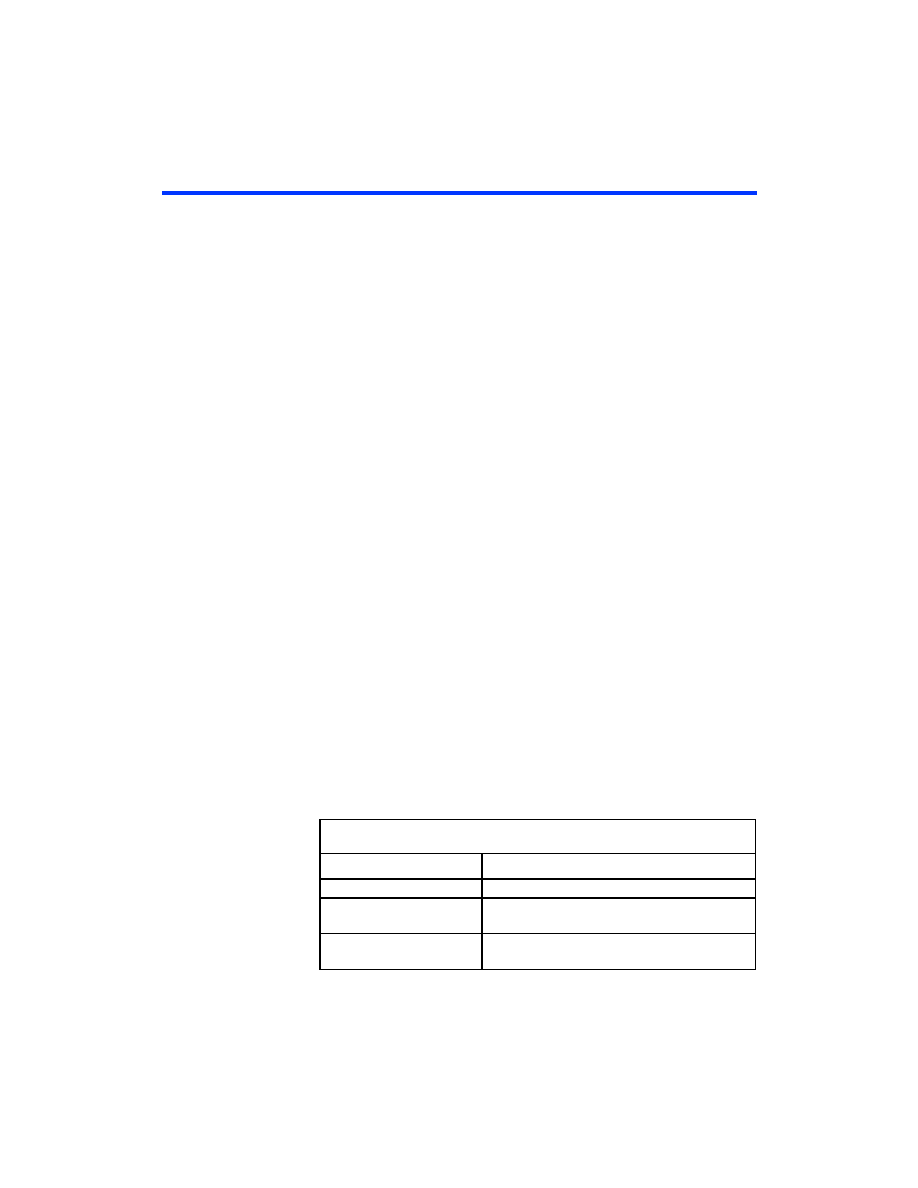

Table 40. Configuration Schemes

Configuration Scheme

Data Source

Configuration device

EPC1 or EPC1441 configuration device

Passive serial (PS)

BitBlaster

TM, ByteBlasterMVTM, or MasterBlasterTM

download cables, or serial data source

Passive serial asynchronous

(PSA)

BitBlaster, ByteBlasterMV, or MasterBlaster

download cables, or serial data source

相关PDF资料 |

PDF描述 |

|---|---|

| EPF6016ATC144-1 | IC FLEX 6000 FPGA 16K 144-TQFP |

| AGM31DTBN-S189 | CONN EDGECARD 62POS R/A .156 SLD |

| A40MX04-1VQG80 | IC FPGA MX SGL CHIP 6K 80-VQFP |

| A40MX04-VQG80I | IC FPGA MX SGL CHIP 6K 80-VQFP |

| AYM31DTBH-S189 | CONN EDGECARD 62POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EPF6016ATC144-2 | 功能描述:FPGA - 现场可编程门阵列 FPGA - Flex 6000 132 LABs 117 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EPF6016ATC144-2N | 功能描述:FPGA - 现场可编程门阵列 FPGA - Flex 6000 132 LABs 117 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EPF6016ATC1443 | 制造商:ALTERA 功能描述:New |

| EPF6016ATC144-3 | 功能描述:FPGA - 现场可编程门阵列 FPGA - Flex 6000 132 LABs 117 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EPF6016ATC144-3N | 功能描述:FPGA - 现场可编程门阵列 FPGA - Flex 6000 132 LABs 117 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。