- 您现在的位置:买卖IC网 > PDF目录19516 > EPM7256AETI100-7 (Altera)IC MAX 7000 CPLD 256 100-TQFP PDF资料下载

参数资料

| 型号: | EPM7256AETI100-7 |

| 厂商: | Altera |

| 文件页数: | 17/64页 |

| 文件大小: | 0K |

| 描述: | IC MAX 7000 CPLD 256 100-TQFP |

| 标准包装: | 270 |

| 系列: | MAX® 7000A |

| 可编程类型: | 系统内可编程 |

| 最大延迟时间 tpd(1): | 7.5ns |

| 电压电源 - 内部: | 3 V ~ 3.6 V |

| 逻辑元件/逻辑块数目: | 16 |

| 宏单元数: | 256 |

| 门数: | 5000 |

| 输入/输出数: | 84 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-TQFP |

| 供应商设备封装: | 100-TQFP(14x14) |

| 包装: | 托盘 |

| 其它名称: | 544-2061 EPM7256AETI100-7-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

24

Altera Corporation

MAX 7000A Programmable Logic Device Data Sheet

Programmable

Speed/Power

Control

MAX 7000A devices offer a power-saving mode that supports low-power

operation across user-defined signal paths or the entire device. This

feature allows total power dissipation to be reduced by 50% or more

because most logic applications require only a small fraction of all gates to

operate at maximum frequency.

The designer can program each individual macrocell in a MAX 7000A

device for either high-speed (i.e., with the Turbo BitTM option turned on)

or low-power operation (i.e., with the Turbo Bit option turned off). As a

result, speed-critical paths in the design can run at high speed, while the

remaining paths can operate at reduced power. Macrocells that run at low

power incur a nominal timing delay adder (tLPA) for the tLAD, tLAC, tIC,

tEN, tSEXP, tACL, and tCPPW parameters.

Output

Configuration

MAX 7000A device outputs can be programmed to meet a variety of

system-level requirements.

MultiVolt I/O Interface

The MAX 7000A device architecture supports the MultiVolt I/O interface

feature, which allows MAX 7000A devices to connect to systems with

differing supply voltages. MAX 7000A devices in all packages can be set

for 2.5-V, 3.3-V, or 5.0-V I/O pin operation. These devices have one set of

VCC

pins for internal operation and input buffers (VCCINT), and another

set for I/O output drivers (VCCIO).

The VCCIO pins can be connected to either a 3.3-V or 2.5-V power supply,

depending on the output requirements. When the VCCIO pins are

connected to a 2.5-V power supply, the output levels are compatible with

2.5-V systems. When the VCCIO pins are connected to a 3.3-V power

supply, the output high is at 3.3 V and is therefore compatible with 3.3-V

or 5.0-V systems. Devices operating with VCCIO levels lower than 3.0 V

incur a slightly greater timing delay of tOD2 instead of tOD1. Inputs can

always be driven by 2.5-V, 3.3-V, or 5.0-V signals.

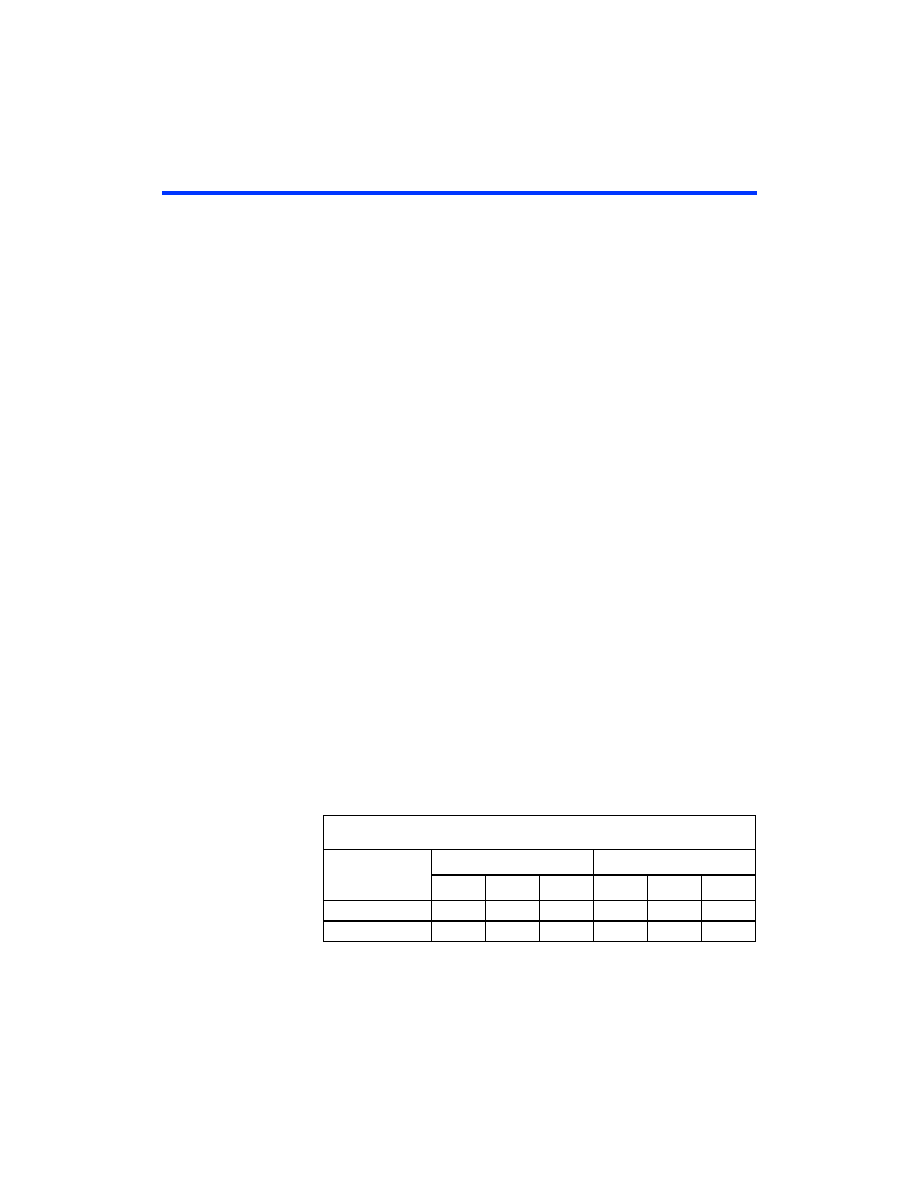

Table 12 describes the MAX 7000A MultiVolt I/O support.

Table 12. MAX 7000A MultiVolt I/O Support

VCCIO Voltage

Input Signal (V)

Output Signal (V)

2.5

3.3

5.0

2.5

3.3

5.0

2.5

vvvv

3.3

vvv

vv

相关PDF资料 |

PDF描述 |

|---|---|

| NPH10S2405EIC | CONV DC/DC 10W 24VIN 5.1VOUT DIP |

| TPSC227K006Y0125 | CAP TANT 220UF 6.3V 10% 2312 |

| EPM7160ELC84-10 | IC MAX 7000 CPLD 160 84-PLCC |

| TMS320DM365ZCE30 | IC DIGITAL MEDIA SOC 338NFBGA |

| EPM7256AETC144-5N | IC MAX 7000 CPLD 256 144-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EPM7256AETI100-7N | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 7000 256 Macro 84 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM7256AETI144-7 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 7000 256 Macro 36 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM7256AETI144-7N | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 7000 256 Macro 36 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM7256AFC256-10 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Altera Corporation 功能描述: |

| EPM7256AFC256-12 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。