- 您现在的位置:买卖IC网 > PDF目录97931 > EPM7512AEQI208-10 PDF资料下载

参数资料

| 型号: | EPM7512AEQI208-10 |

| 文件页数: | 16/60页 |

| 文件大小: | 1041K |

| 代理商: | EPM7512AEQI208-10 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

Altera Corporation

23

MAX 7000A Programmable Logic Device Data Sheet

Power

Sequencing &

Hot-Socketing

Because MAX 7000A devices can be used in a mixed-voltage

environment, they have been designed specifically to tolerate any possible

power-up sequence. The VCCIO and VCCINT power planes can be powered

in any order.

Signals can be driven into MAX 7000AE devices before and during power-

up (and power-down) without damaging the device. Additionally,

MAX 7000AE devices do not drive out during power-up. Once operating

conditions are reached, MAX 7000AE devices operate as specified by the

user.

Design Security

All MAX 7000A devices contain a programmable security bit that controls

access to the data programmed into the device. When this bit is

programmed, a design implemented in the device cannot be copied or

retrieved. This feature provides a high level of design security because

programmed data within EEPROM cells is invisible. The security bit that

controls this function, as well as all other programmed data, is reset only

when the device is reprogrammed.

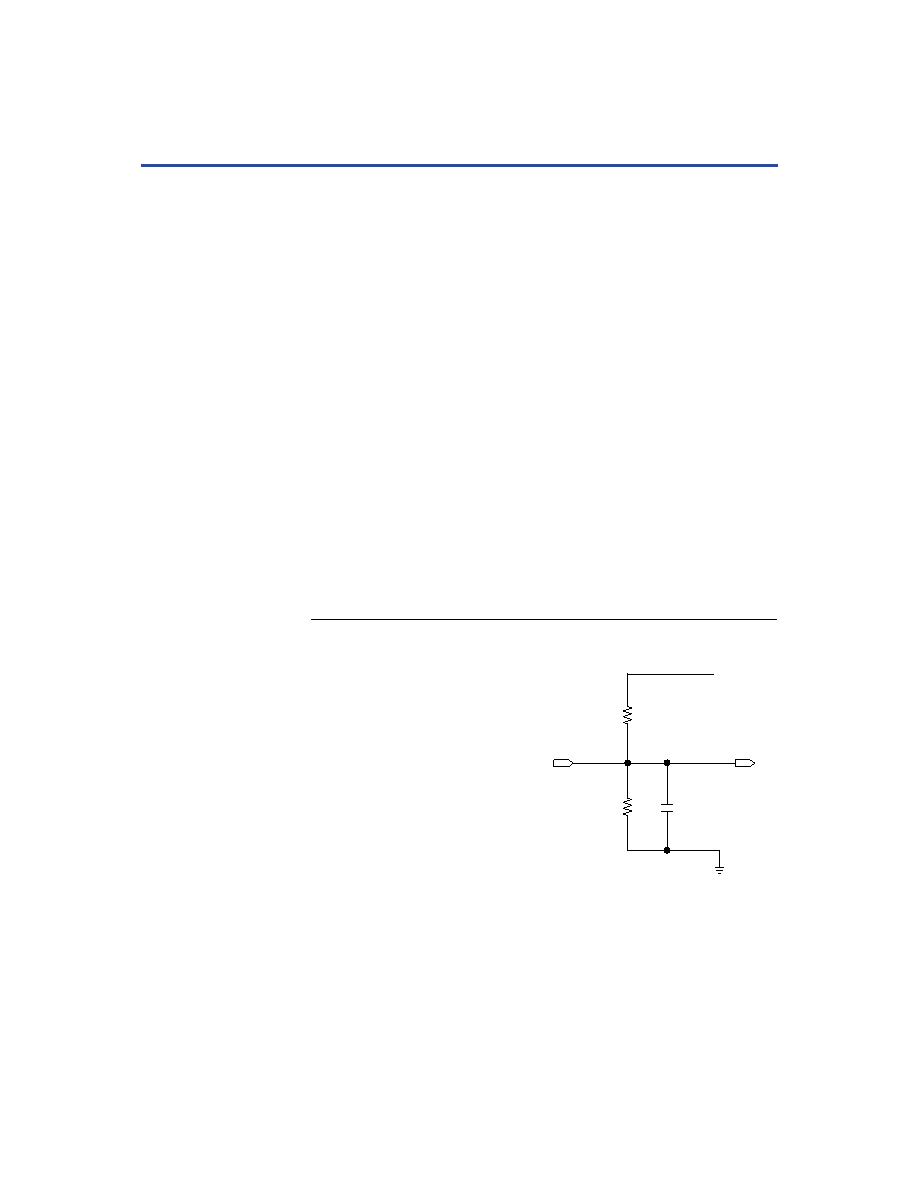

Generic Testing

MAX 7000A devices are fully tested. Complete testing of each

programmable EEPROM bit and all internal logic elements ensures 100%

programming yield. AC test measurements are taken under conditions

equivalent to those shown in Figure 9. Test patterns can be used and then

erased during early stages of the production flow.

Figure 9. MAX 7000A AC Test Conditions

VCC

To Test

System

C1 (includes jig

capacitance)

Device input

rise and fall

times < 2 ns

Device

Output

703

[521 ]

586

[481 ]

Power supply transients can affect AC

measurements. Simultaneous transitions

of multiple outputs should be avoided for

accurate measurement. Threshold tests

must not be performed under AC

conditions. Large-amplitude, fast-ground-

current transients normally occur as the

device outputs discharge the load

capacitances. When these transients ow

through the parasitic inductance between

the device ground pin and the test system

ground, signicant reductions in

observable noise immunity can result.

Numbers in brackets are for 2.5-V

outputs. Numbers without brackets are for

3.3-V outputs.

相关PDF资料 |

PDF描述 |

|---|---|

| EPM7512AETC144-10 | |

| EPM7512AETC144-12 | |

| EPM7512AETC144-7 | |

| EPM7032AELC44-5 | Electrically-Erasable Complex PLD |

| EPM7032AELI44-5 | Electrically-Erasable Complex PLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EPM7512AEQI208-10N | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 7000 512 Macro 176 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM7512AETC100-10 | 制造商:ALTERA 制造商全称:Altera Corporation 功能描述:High-performance 3.3-V EEPROM-based programmable logic devices (PLDs) built on second-generation Multiple Array MatriX |

| EPM7512AETC14410 | 制造商:Altera Corporation 功能描述: |

| EPM7512AETC144-10 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 7000 512 Macro 36 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM7512AETC144-10N | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 7000 512 Macro 36 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。