- 您现在的位置:买卖IC网 > PDF目录16870 > EVAL-AD2S1210EDZ (Analog Devices Inc)BOARD EVAL AD2S1210 PDF资料下载

参数资料

| 型号: | EVAL-AD2S1210EDZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 2/36页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL AD2S1210 |

| 标准包装: | 1 |

| 主要目的: | 接口,旋转变压至数字 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | AD2S1210 |

| 主要属性: | 10 ~ 16 位分辨率,3125 rps 最大(10 位)或 1024 脉冲 |

| 次要属性: | 图形用户界面 |

| 已供物品: | 板,CD |

| 产品目录页面: | 788 (CN2011-ZH PDF) |

| 相关产品: | AD2S1210CSTZ-ND - IC CONV R/D VAR RES OSC 48-LQFP AD2S1210BSTZ-ND - IC CONV R/D 10-16BIT 48-LQFP AD2S1210ASTZ-ND - IC CONV R/D 10-16BIT 48-LQFP |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

AD2S1210

Rev. A | Page 10 of 36

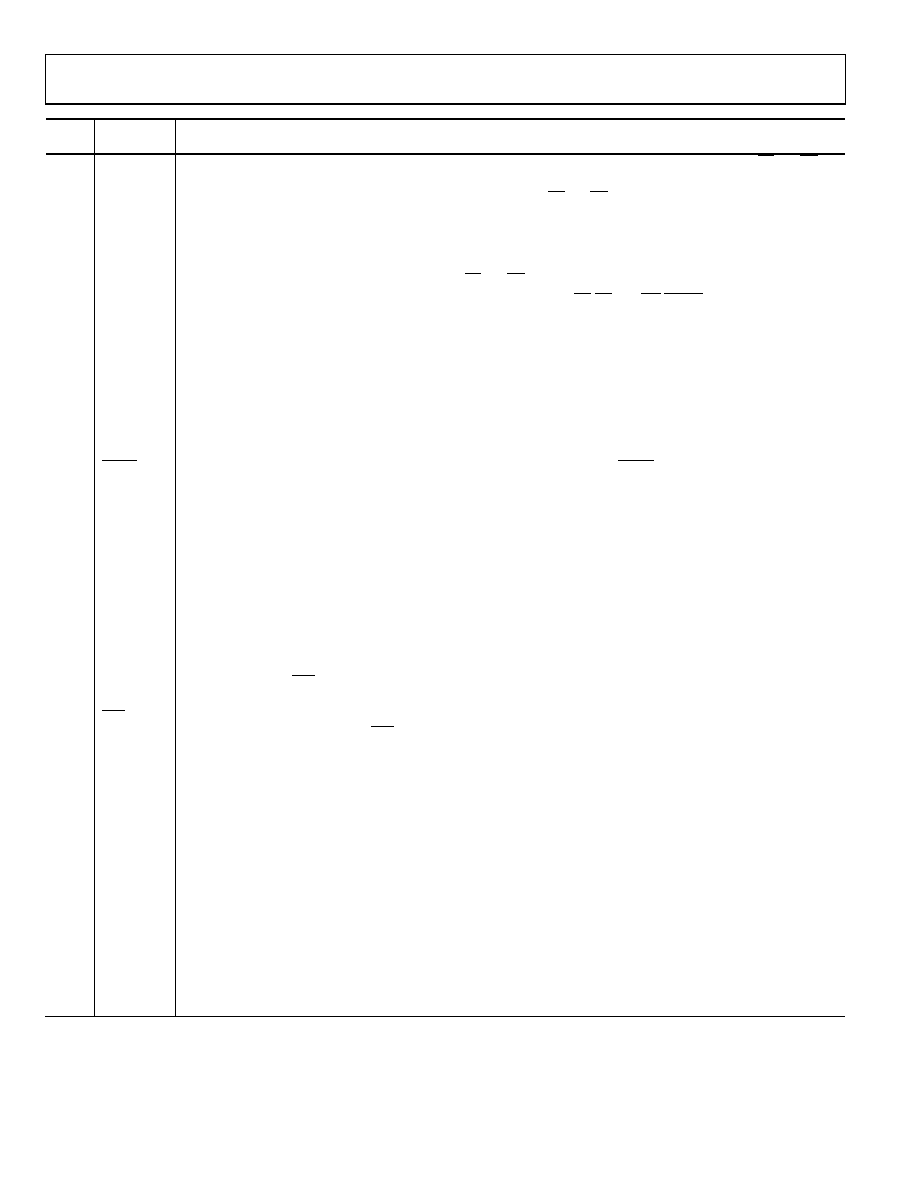

Pin

No.

Mnemonic

Description

13

DB13/SCLK

Data Bit 13/Serial Clock. In parallel mode, this pin acts as DB13, a three-state data output pin controlled by CS and RD. In

serial mode, this pin acts as the serial clock input.

14 to

17

DB12 to

DB9

Data Bit 12 to Data Bit 9. Three-state data output pins controlled by CS and RD.

18

VDRIVE

Logic Power Supply Input. The voltage supplied at this pin determines at what voltage the interface operates.

Decouple this pin to DGND. The voltage range on this pin is 2.3 V to 5.25 V and may be different to the voltage range

at AVDD and DVDD but should never exceed either by more than 0.3 V.

20

DB8

Data Bit 8. Three-state data output pin controlled by CS and RD.

21 to

28

DB7 to DB0

Data Bit 7 to Data Bit 0. Three-state data input/output pins controlled by CS, RD, and WR/FSYNC.

29

A

Incremental Encoder Emulation Output A. Logic output. This output is free running and is valid if the resolver format

input signals applied to the converter are valid.

30

B

Incremental Encoder Emulation Output B. Logic output. This output is free running and is valid if the resolver format

input signals applied to the converter are valid.

31

NM

North Marker Incremental Encoder Emulation Output. Logic output. This output is free running and is valid if the

resolver format input signals applied to the converter are valid.

32

DIR

Direction. Logic output. This output is used in conjunction with the incremental encoder emulation outputs. The DIR

output indicates the direction of the input rotation and is high for increasing angular rotation.

33

RESET

Reset. Logic input. The AD2S1210 requires an external reset signal to hold the RESET input low until VDD is within the

specified operating range of 4.75 V to 5.25 V.

34

LOT

Loss of Tracking. Logic output. LOT is indicated by a logic low on the LOT pin and is not latched. Refer to the Loss of

Position Tracking Detection section.

35

DOS

Degradation of Signal. Logic output. Degradation of signal (DOS) is detected when either resolver input (sine or cosine)

exceeds the specified DOS sine/cosine threshold or when an amplitude mismatch occurs between the sine and

cosine input voltages. DOS is indicated by a logic low on the DOS pin. Refer to the Signal Degradation Detection

section.

36

A1

Mode Select 1. Logic input. A1 in conjunction with A0 allows the mode of the AD2S1210 to be selected. Refer to the

Configuration of AD2S1210 section.

37

A0

Mode Select 0. Logic input. A0 in conjunction with A1 allows the mode of the AD2S1210 to be selected. Refer to the

Configuration of AD2S1210 section.

38

EXC

Excitation Frequency. Analog output. An on-board oscillator provides the sinusoidal excitation signal (EXC) and its

complement signal (EXC) to the resolver. The frequency of this reference signal is programmable via the excitation

frequency register.

39

EXC

Excitation Frequency Complement. Analog output. An on-board oscillator provides the sinusoidal excitation signal

(EXC) and its complement signal (EXC) to the resolver. The frequency of this reference signal is programmable via the

excitation frequency register.

40

AGND

Analog Ground. This pin is the ground reference points for analog circuitry on the AD2S1210. Refer all analog input

signals and any external reference signal to this AGND voltage. Connect the AGND pin to the AGND plane of a

system. The AGND and DGND voltages should ideally be at the same potential and must not be more than 0.3 V

apart, even on a transient basis.

41

SIN

Positive Analog Input of Differential SIN/SINLO Pair. The input range is 2.3 V p-p to 4.0 V p-p.

42

SINLO

Negative Analog Input of Differential SIN/SINLO Pair. The input range is 2.3 V p-p to 4.0 V p-p.

43

AVDD

Analog Supply Voltage, 4.75 V to 5.25 V. This pin is the supply voltage for all analog circuitry on the AD2S1210. The

AVDD and DVDD voltages ideally should be at the same potential and must not be more than 0.3 V apart, even on a

transient basis.

44

COSLO

Negative Analog Input of Differential COS/COSLO Pair. The input range is 2.3 V p-p to 4.0 V p-p.

45

COS

Positive Analog Input of Differential COS/COSLO Pair. The input range is 2.3 V p-p to 4.0 V p-p.

46

REFBYP

Reference Bypass. Connect reference decoupling capacitors at this pin. Typical recommended values are 10 μF and 0.01 μF.

47

REFOUT

Voltage Reference Output.

48

RES0

Resolution Select 0. Logic input. RES0 in conjunction with RES1 allows the resolution of the AD2S1210 to be

programmed. Refer to the Configuration of AD2S1210 section.

相关PDF资料 |

PDF描述 |

|---|---|

| MAX6162AESA+T | IC VREF SERIES PREC 2.048V 8SOIC |

| 207W234-3-0 | BOOT MOLDED |

| RP40-2412DGW/N-HC | CONV DC/DC 40W 9-36VIN +/-12VOUT |

| V110B5C100BL2 | CONVERTER MOD DC/DC 5V 100W |

| ADR370ARTZ-REEL7 | IC VREF SERIES PREC SOT-23-3 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD4001FMCZ | 功能描述:EVAL BOARD FOR AD4001 制造商:analog devices inc. 系列:- 零件状态:在售 A/D 转换器数:1 位数:16 采样率(每秒):2M 数据接口:SPI,DSP 输入范围:±VREF 不同条件下的功率(典型值):20mW @ 2MSPS 使用的 IC/零件:AD4001 所含物品:板,电源 标准包装:1 |

| EVAL-AD421EB | 制造商:AD 制造商全称:Analog Devices 功能描述:Loop-Powered 4 mA to 20 mA DAC |

| EVAL-AD5025EBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Fully Accurate 12-/14-/16-Bit VOUT DAC SPI Interface 2.7 V to 5.5 V in a TSSOP |

| EVAL-AD5045EBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Fully Accurate 12-/14-/16-Bit VOUT DAC SPI Interface 2.7 V to 5.5 V in a TSSOP |

| EVAL-AD5060EB | 制造商:Analog Devices 功能描述:EVAL BD FOR AD506X DAC 14-/16BIT, SERL INPUT - Bulk |

发布紧急采购,3分钟左右您将得到回复。