- 您现在的位置:买卖IC网 > PDF目录16598 > EVAL-AD5232SDZ (Analog Devices Inc)BOARD EVAL FOR AD5232 PDF资料下载

参数资料

| 型号: | EVAL-AD5232SDZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 19/24页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD5232 |

| 标准包装: | 1 |

| 主要目的: | 数字电位器 |

| 已用 IC / 零件: | AD5232 |

| 主要属性: | 2 通道,256 位置 |

| 次要属性: | SPI 接口 |

| 已供物品: | 板,CD |

AD5232

Data Sheet

Rev. C | Page 4 of 24

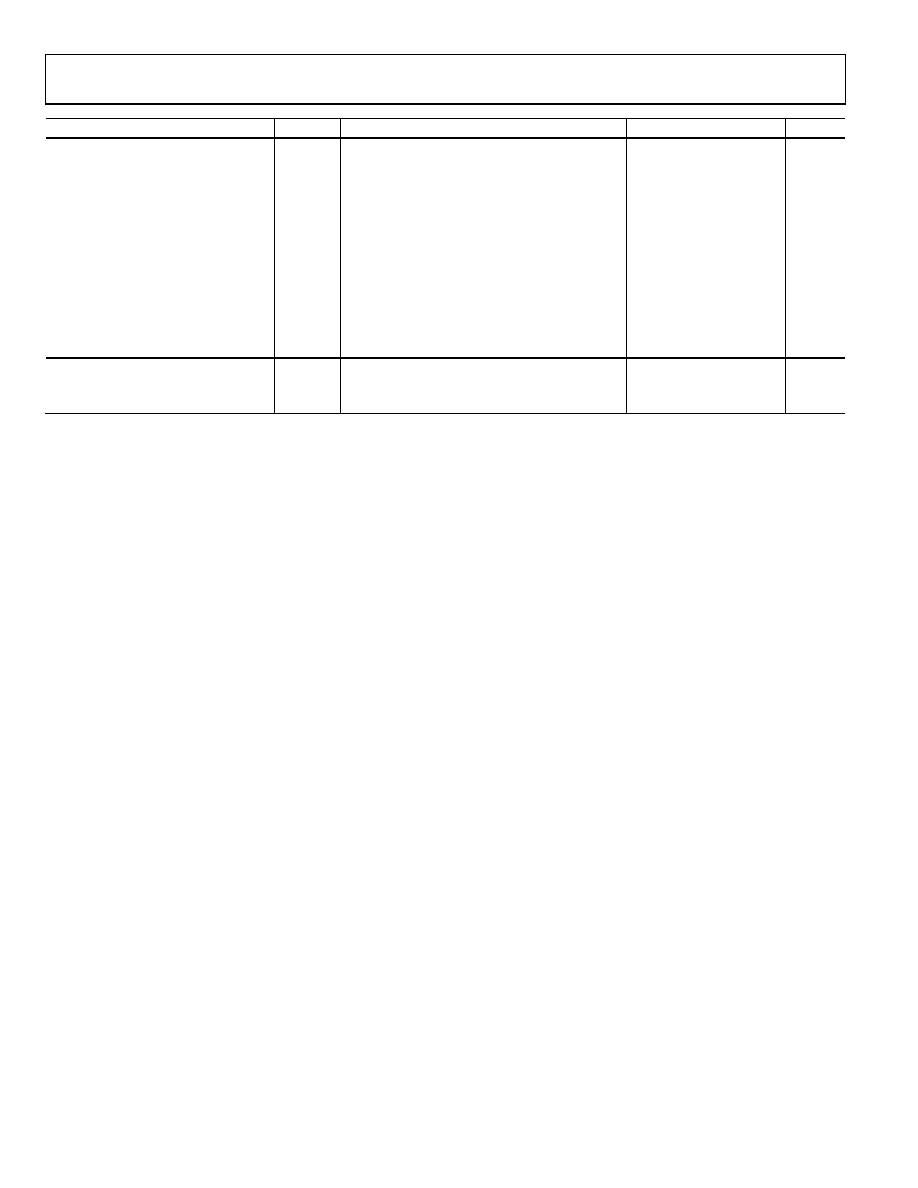

Parameter

Symbol

Conditions

Min

Typ1

Max

Unit

DYNAMIC CHARACTERISTICS5, 9

Bandwidth

3 dB, BW_10k, R = 10 k

500

kHz

Total Harmonic Distortion

THDw

VA = 1 V rms, VB = 0 V, f = 1 kHz, RAB = 10 k

0.022

%

VA = 1 V rms, VB = 0 V, f = 1 kHz, RAB = 50 k, 100 k

0.045

%

VW Settling Time

tS

VDD = 5 V, VSS = 0 V, VA = VDD, VB = 0 V,

0.65/3/6

s

VW = 0.50% error band, Code 0x00 to Code 0x80

for RAB = 10 k/50 k/100 k

Resistor Noise Voltage

eN_WB

RWB = 5 k, f= 1 kHz

9

nV/√Hz

Crosstalk (CW1/CW2)

CT

VA = VDD, VB = 0 V, measure VW with

5

nV-sec

adjacent VR making full-scale code change

Analog Crosstalk (CW1/CW2)

CTA

VA1 = VDD, VB1 = 0 V, measure VW1 with VW2 =

70

dB

5 V p-p @ f = 10 kHz; Code1 = 0x80; Code2 = 0xFF

FLASH/EE MEMORY RELIABILITY

Endurance10

100

kCycles

Data Retention11

100

Years

1

Typical parameters represent average readings at 25°C and VDD = 5 V.

2

Resistor position nonlinearity (R-INL) error is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper

positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. IW ~ 50 A @ VDD = 2.7 V and IW ~

400 A @ VDD = 5 V for the RAB = 10 k version, IW ~ 50 A for the RAB = 50 k version, and IW ~ 25 A for the RAB = 100 k version (see Figure 22).

3

INL and DNL are measured at VW with the RDACx configured as a potentiometer divider similar to a voltage output digital-to-analog converter. VA = VDD and VB = VSS.

DNL specification limits of ±1 LSB maximum are guaranteed monotonic operating conditions (see Figure 23).

4

The A, B, and W resistor terminals have no limitations on polarity with respect to each other. Dual supply operation enables ground-referenced bipolar signal

adjustment.

5

Guaranteed by design; not subject to production test.

6

Common-mode leakage current is a measure of the dc leakage from any A, B, or W terminal to a common-mode bias level of VDD/2.

7

Transfer (XFR) mode current is not continuous. Current is consumed while the EEMEMx locations are read and transferred to the RDACx register (see Figure 13).

8

PDISS is calculated from (IDD × VDD) + (ISS × VSS).

9

All dynamic characteristics use VDD = +2.5 V and VSS = 2.5 V, unless otherwise noted.

10

Endurance is qualified to 100,000 cycles per JEDEC Std. 22, Method A117 and measured at 40°C, +25°C, and +85°C. Typical endurance at +25°C is 700,000 cycles.

11

The retention lifetime equivalent at junction temperature (TJ) = 55°C, as per JEDEC Std. 22, Method A117. Retention lifetime, based on an activation energy of 0.6 eV,

derates with junction temperature as shown in Figure 44 in the Flash/EEMEM Reliability section. The AD5232 contains 9,646 transistors. Die size = 69 mil × 115 mil,

7,993 sq. mil.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-BN0-EW | CONVERTER MOD DC/DC 5V 100W |

| VE-B6R-EW | CONVERTER MOD DC/DC 7.5V 100W |

| 6-837975-6 | LGH-3 LEAD ELECT MLD END |

| S1210R-153K | INDUCTOR SHIELDED 15UH SMD |

| S1210-122K | INDUCTOR SHIELDED 1.2UH SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD5232-SDZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Nonvolatile Memory,Dual 256-Position Digital Potentiometer |

| EVAL-AD5233SDZ | 功能描述:BOARD EVAL FOR AD5233 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-AD5235EBZ | 制造商:Analog Devices 功能描述:EVALUATION BOARD FOR 1024-POSITION DIGITAL POTENTIOMETER 制造商:Analog Devices 功能描述:EVAL BD FOR 1024-POSITION DGTL POTENTIOMETER - Bulk |

| EVAL-AD5235SDZ | 功能描述:BOARD EVAL FOR AD5235 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-AD5235SDZ | 制造商:Analog Devices 功能描述:Evaluation board |

发布紧急采购,3分钟左右您将得到回复。