- 您现在的位置:买卖IC网 > PDF目录17075 > EVAL-AD5391EBZ (Analog Devices Inc)BOARD EVALUATION FOR AD5391 PDF资料下载

参数资料

| 型号: | EVAL-AD5391EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 17/44页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD5391 |

| 产品培训模块: | DAC Architectures |

| 标准包装: | 1 |

| DAC 的数量: | 16 |

| 位数: | 12 |

| 采样率(每秒): | 167k |

| 数据接口: | 串行 |

| 设置时间: | 6µs |

| DAC 型: | 电压 |

| 工作温度: | -40°C ~ 85°C |

| 已供物品: | 板,CD |

| 已用 IC / 零件: | AD5391 |

| 相关产品: | AD5391BSTZ-5-ND - IC DAC 12BIT 16CHAN 3V 52LQFP AD5391BSTZ-3-ND - IC DAC 12BIT 16CHAN 3V 52LQFP AD5391BCPZ-5-REEL7-ND - IC DAC 12BIT 16CHAN 5V 64LFCSP AD5391BCPZ-5-REEL-ND - IC DAC 12BIT 16CHAN 5V 64-LFCSP AD5391BCPZ-3-ND - IC DAC 12BIT I2C 16CH 3V 64LFCSP AD5391BCPZ-5-ND - IC DAC 12BIT 16CH 5V 64-LFCSP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD5390/AD5391/AD5392

Data Sheet

Rev. E | Page 24 of 44

DATA DECODING

AD5390/AD5392

The AD5390/AD5392 contain an internal 14-bit data bus.

The input data is decoded depending on the data loaded to

the REG1 and REG0 bits of the input serial register. This is

shown in Table 10.

Data from the serial input register is loaded into the addressed

DAC input register, offset (c) register, or gain (m) register. The

format data, and the offset (c) and gain (m) register contents

are shown in Table 11 to Table 13.

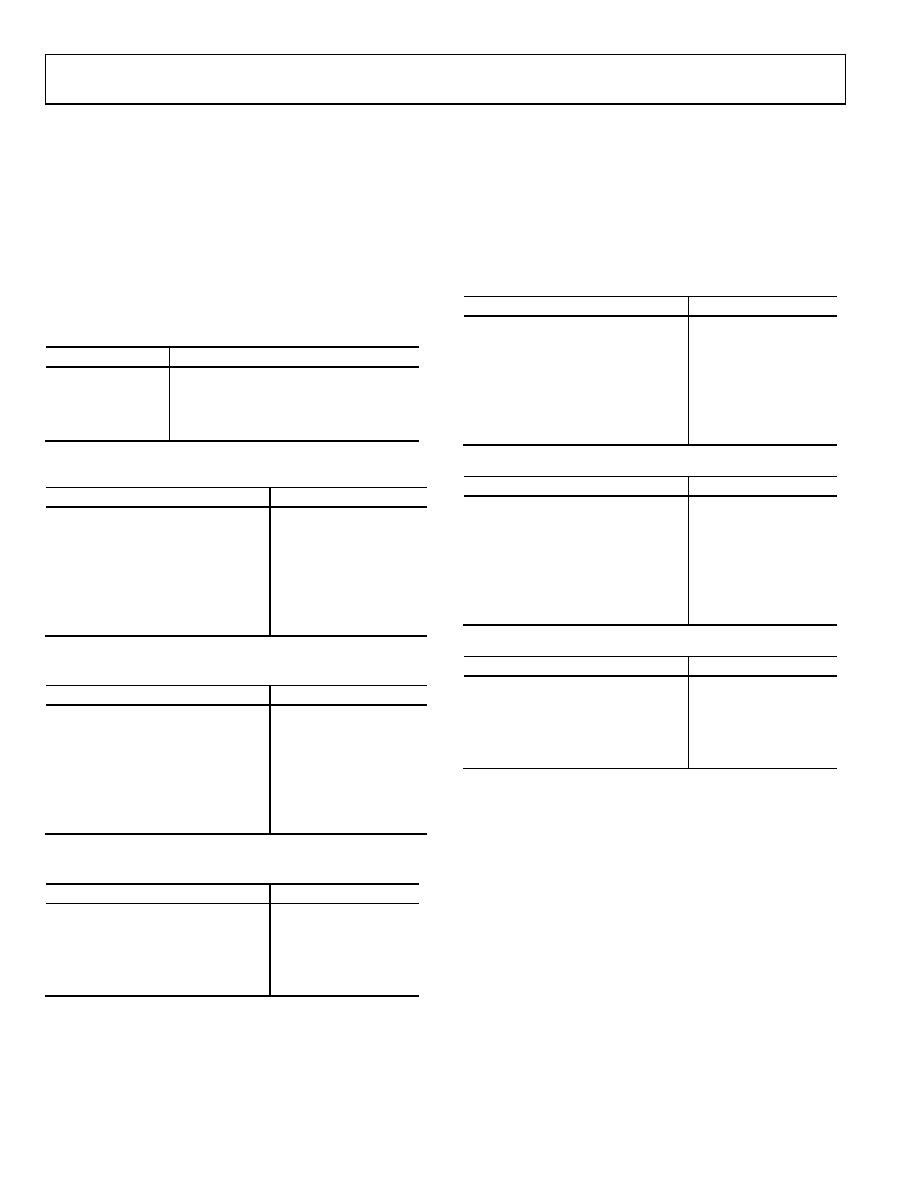

Table 10. Register Selection

REG1

REG0

Register Selected

1

Input data register (x1)

1

0

Offset register (c)

0

1

Gain register (m)

0

Special function registers (SFRs)

Table 11. AD5390/AD5392 DAC Data Format

(REG1 = 1, REG0 = 1)

DB13 to DB0

DAC Output (V)

11 1111

1111

2 VREF × (16383/16384)

11 1111

1111

1110

2 VREF × (16382/16384)

10 0000

0000

0001

2 VREF × (8193/16384)

10 0000

0000

2 VREF × (8192/16384)

01 1111

1111

2 VREF × (8191/16384)

00 0000

0000

0001

2 VREF × (1/16384)

00 0000

0000

0

Table 12. AD5390/AD5392 Offset Data Format

(REG1 = 1, REG0 = 0)

DB13 to DB0

Offset (LSB)

111111

1111

+8191

111111

1111

1110

+8190

100000

0000

0001

+1

100000

0000

+0

011111

1111

–1

000000

0000

0001

–8191

000000

0000

–8192

Table 13. AD5390/AD5392 Gain Data Format

(REG1 = 0, REG0 = 1)

DB13 to DB0

Gain Factor

11 1111

1111

1110

1

10 1111

1111

1110

0.75

01 1111

1111

1110

0.5

00 1111

1111

1110

0.25

00 0000

0000

0

AD5391

The AD5391 contains an internal 12-bit data bus. The input

data is decoded depending on the value loaded to the REG1 and

REG0 bits of the input serial register. The input data from the

serial input register is loaded into the addressed DAC input

register, offset (c) register, or gain (m) register. The format data

and the offset (c) and gain (m) register contents are shown in

Table 14. AD5391 DAC Data Format (REG1 = 1, REG0 = 1)

DB11 to DB0

DAC Output (V)

1111

2 VREF × (4095/4096)

1111

1110

2 VREF × (4094/4096)

1000

0000

0001

2 VREF × (2049/4096)

1000

0000

2 VREF × (2048/4096)

0111

1111

2 VREF × (2047/4096)

0000

0001

2 VREF × (1/4096)

0000

0

Table 15. AD5391 Offset Data Format (REG1 = 1, REG0 = 0)

DB11 to DB0

Offset (LSB)

1111

+2047

1111

1110

+2046

1000

0000

0001

+1

1000

0000

+0

0111

1111

–1

0000

0001

–2047

0000

–2048

Table 16. AD5391 Gain Data Format (REG1 = 0, REG0 = 1)

DB11 to DB0

Gain Factor

1111

1110

1

1011

1111

1110

0.75

0111

1111

1110

0.5

0011

1111

1110

0.25

0000

0

相关PDF资料 |

PDF描述 |

|---|---|

| EMA10DTBH | CONN EDGECARD 20POS R/A .125 SLD |

| EVAL-AD5372EBZ | BOARD EVAL FOR AD5372 |

| EVAL-AD5361EBZ | BOARD EVAL FOR AD5361 |

| V300C2E50BF3 | CONVERTER MOD DC/DC 2V 50W |

| 0210490910 | CABLE JUMPER 1.25MM .178M 21POS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD5392EB | 制造商:Analog Devices 功能描述:EVAL BD FOR 8-/16CH, 3V/5 V, SERL INPUT, SGL-SUPPLY,12-/14BI - Bulk |

| EVAL-AD5392EBZ | 功能描述:BOARD EVAL FOR AD5392 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5398AEBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:120 mA, Current Sinking, 10-Bit, I2C DAC |

| EVAL-AD5398EB | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk 制造商:Rochester Electronics LLC 功能描述: |

| EVAL-AD5398EBZ | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk |

发布紧急采购,3分钟左右您将得到回复。