- 您现在的位置:买卖IC网 > PDF目录17076 > EVAL-AD5754REBZ (Analog Devices Inc)BOARD EVAL FOR AD5754R PDF资料下载

参数资料

| 型号: | EVAL-AD5754REBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 29/32页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD5754R |

| 标准包装: | 1 |

| DAC 的数量: | 4 |

| 位数: | 16 |

| 采样率(每秒): | * |

| 数据接口: | 串行 |

| 设置时间: | 10µs |

| DAC 型: | 电压 |

| 工作温度: | -40°C ~ 85°C |

| 已供物品: | 板 |

| 已用 IC / 零件: | AD5754 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页

AD5724R/AD5734R/AD5754R

Rev. E | Page 6 of 32

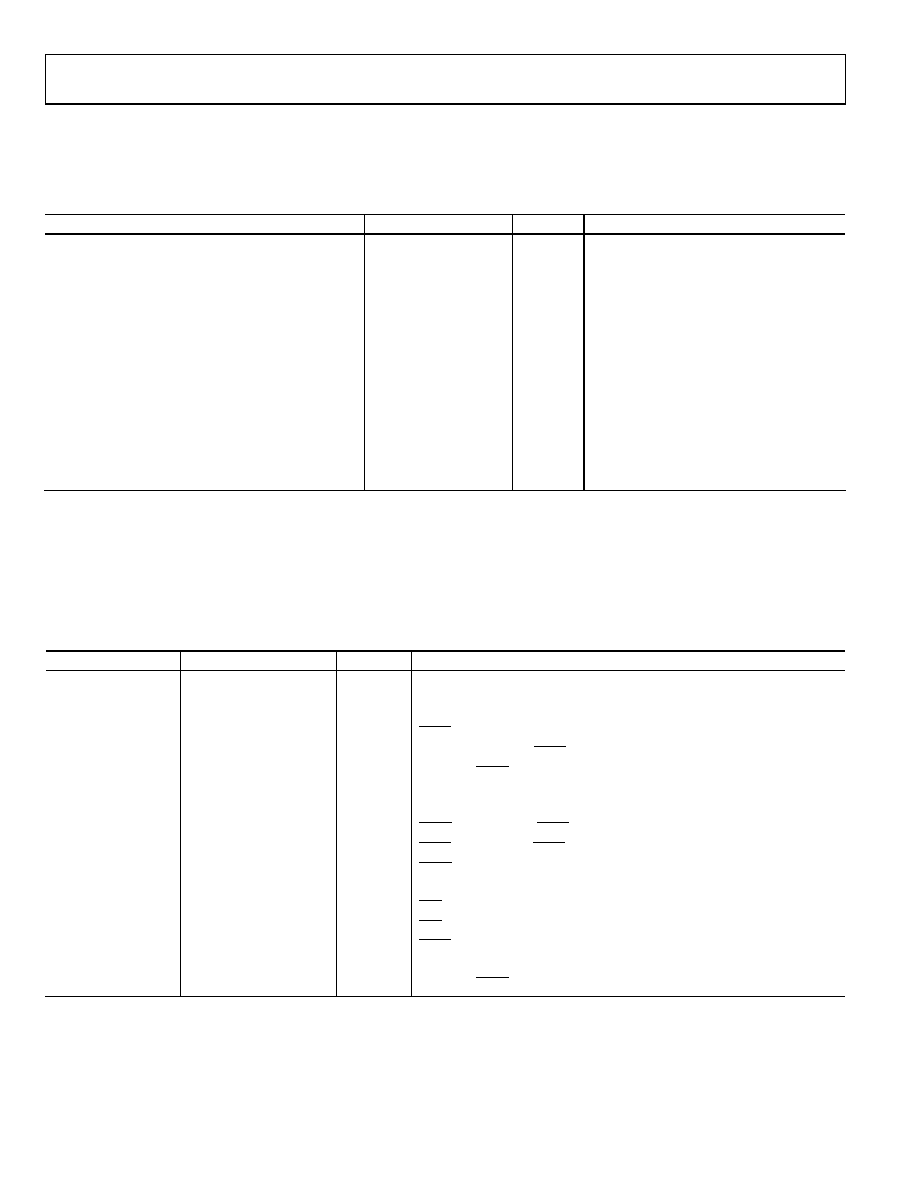

AC PERFORMANCE CHARACTERISTICS

AVDD = 4.5 V1 to 16.5 V, AVSS = 4.5 V1 to 16.5 V or 0 V, GND = 0 V, REFIN= 2.5 V external, DVCC = 2.7 V to 5.5 V, RLOAD = 2 kΩ,

CLOAD = 200 pF, all specifications TMIN to TMAX, unless otherwise noted.

Table 3.

Min

Typ

Max

Unit

Test Conditions/Comments

DYNAMIC PERFORMANCE

Output Voltage Settling Time

10

12

μs

20 V step to ±0.03 % FSR

7.5

8.5

μs

10 V step to ±0.03 % FSR

5

μs

512 LSB step settling (16-bit resolution)

Slew Rate

3.5

V/μs

Digital-to-Analog Glitch Energy

13

nV-sec

Glitch Impulse Peak Amplitude

35

mV

Digital Crosstalk

10

nV-sec

DAC-to-DAC Crosstalk

10

nV-sec

Digital Feedthrough

0.6

nV-sec

Output Noise

0.1 Hz to 10 Hz Bandwidth

15

μV p-p

0x8000 DAC code

100 kHz Bandwidth

80

μV rms

Output Noise Spectral Density

320

nV/√Hz

Measured at 10 kHz, 0x8000 DAC code

1 For specified performance, headroom requirement is 0.9 V.

2 Guaranteed by design and characterization; not production tested.

TIMING CHARACTERISTICS

AVDD = 4.5 V to 16.5 V, AVSS = 4.5 V to 16.5 V or 0 V, GND = 0 V, REFIN = 2.5 V external, DVCC = 2.7 V to 5.5 V, RLOAD = 2 kΩ,

CLOAD = 200 pF, all specifications are TMIN to TMAX, unless otherwise noted.

Table 4.

Limit at TMIN, TMAX

Unit

Description

33

ns min

SCLK cycle time

t2

13

ns min

SCLK high time

t3

13

ns min

SCLK low time

t4

13

ns min

SYNC falling edge to SCLK falling edge setup time

t5

13

ns min

SCLK falling edge to SYNC rising edge

t6

100

ns min

Minimum SYNC high time (write mode)

t7

7

ns min

Data setup time

t8

2

ns min

Data hold time

t9

20

ns min

LDAC falling edge to SYNC falling edge

t10

130

ns min

SYNC rising edge to LDAC falling edge

t11

20

ns min

LDAC pulse width low

t12

10

μs typ

DAC output settling time

t13

20

ns min

CLR pulse width low

t14

2.5

μs max

CLR pulse activation time

t155

13

ns min

SYNC rising edge to SCLK falling edge

t165

40

ns max

SCLK rising edge to SDO valid (CL SDO6 = 15 pF)

t17

200

ns min

Minimum SYNC high time (readback/daisy-chain mode)

1 Guaranteed by characterization; not production tested.

2 All input signals are specified with tR = tF = 5 ns (10% to 90% of DVCC) and timed from a voltage level of 1.2 V.

3 See Figure 2, Figure 3, and Figure 4.

4 To accommodate t16, in readback and daisy-chain modes the SCLK cycle time must be increased to 90 ns.

5 Daisy-chain and readback mode.

6 CL SDO = capacitive load on SDO output.

相关PDF资料 |

PDF描述 |

|---|---|

| NRS5020T6R8MMGJ | INDUCTOR 6.8UH 1.65A 20% SMD |

| AP2146MPG-13 | IC USB PWR SWITCH .5A DUAL 8MSOP |

| 380LX472M035J012 | CAP ALUM 4700UF 35V 20% SNAP |

| EVAL-AD5443SDZ | BOARD EVAL FOR AD5443 |

| ESA10DTBD | CONN EDGECARD 20POS R/A .125 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD5755-1SDZ | 功能描述:BOARD EVAL FOR AD5755-1 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5755SDZ | 功能描述:BOARD EVAL FOR AD5755 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5757SDZ | 功能描述:BOARD EVAL FOR AD5757 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5760SDZ | 功能描述:BOARD EVAL FOR AD5760SDZ RoHS:否 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5764EB | 制造商:Analog Devices 功能描述:EVALUATION BOARD FOR QUAD, 16-BIT, HIGH ACCURACY, SERIAL INPUT, BIPOLAR VOLTAGE OUTPUT DAC 制造商:Analog Devices 功能描述:EVALUATION CONTROL BOARD I.C. - Bulk |

发布紧急采购,3分钟左右您将得到回复。