- 您现在的位置:买卖IC网 > PDF目录17046 > EVAL-AD7606EDZ (Analog Devices Inc)EVAL BOARD FOR AD7606 PDF资料下载

参数资料

| 型号: | EVAL-AD7606EDZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 7/36页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR AD7606 |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 16 |

| 采样率(每秒): | 200k |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 在以下条件下的电源(标准): | 100mW @ 200kSPS |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD7606 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

Data Sheet

AD7606/AD7606-6/AD7606-4

Rev. C | Page 15 of 36

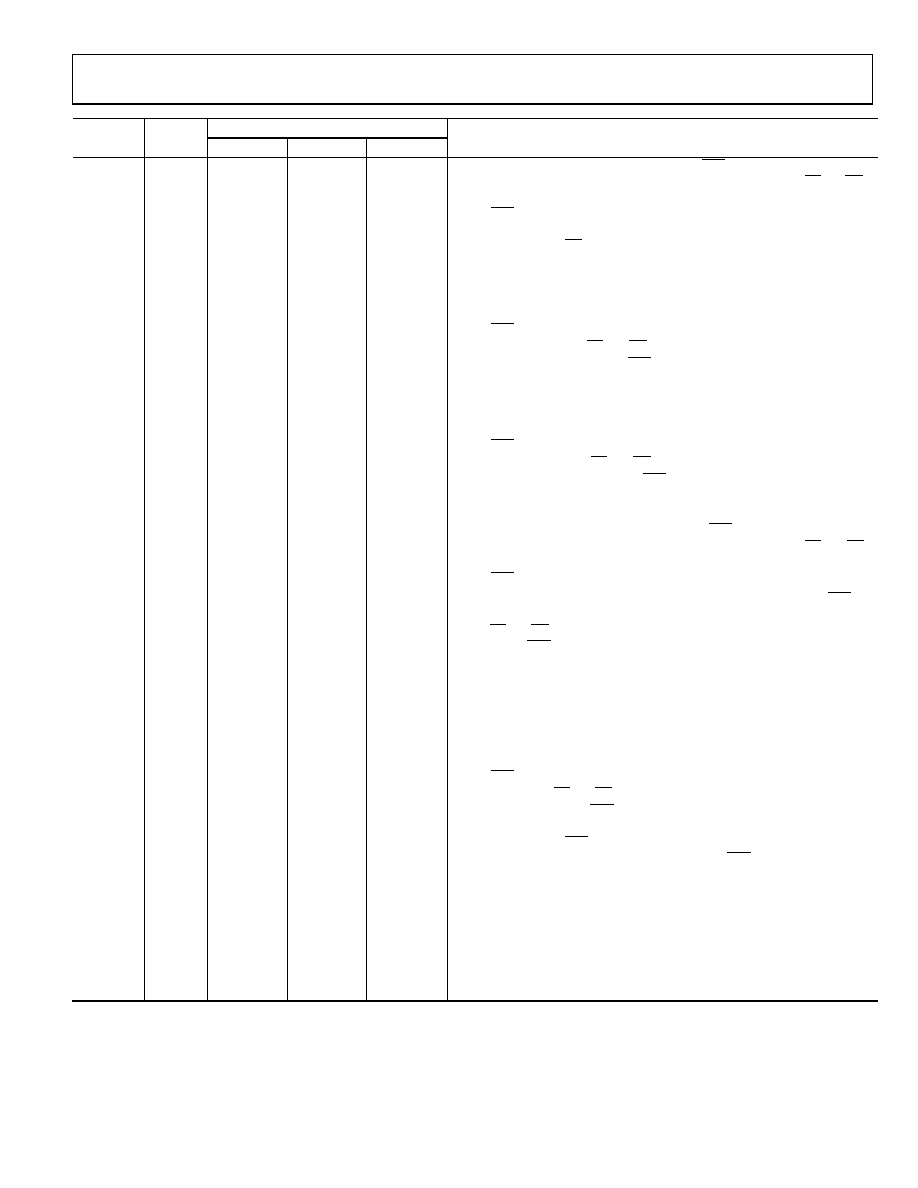

Pin No.

Type1

Mnemonic

Description

AD7606

AD7606-6

AD7606-4

22 to 16

DO

DB[6:0]

Parallel Output Data Bits, DB6 to DB0. When PAR/SER/BYTE SEL = 0, these

pins act as three-state parallel digital input/output pins. When CS and RD

are low, these pins are used to output DB6 to DB0 of the conversion result.

When PAR/SER/BYTE SEL = 1, these pins should be tied to AGND. When

operating in parallel byte interface mode, DB[7:0] outputs the 16-bit con-

version result in two RD operations. DB7 (Pin 24) is the MSB; DB0 is the LSB.

23

P

VDRIVE

Logic Power Supply Input. The voltage (2.3 V to 5.25 V) supplied at this pin

determines the operating voltage of the interface. This pin is nominally at the

same supply as the supply of the host interface (that is, DSP and FPGA).

24

DO

DB7/DOUTA

Parallel Output Data Bit 7 (DB7)/Serial Interface Data Output Pin (DOUTA).

When PAR/SER/BYTE SEL = 0, this pins acts as a three-state parallel digital

input/output pin. When CS and RD are low, this pin is used to output DB7

of the conversion result. When PAR/SER/BYTE SEL = 1, this pin functions

section for more details). When operating in parallel byte mode, DB7 is

the MSB of the byte.

25

DO

DB8/DOUTB

Parallel Output Data Bit 8 (DB8)/Serial Interface Data Output Pin (DOUTB).

When PAR/SER/BYTE SEL = 0, this pin acts as a three-state parallel digital

input/output pin. When CS and RD are low, this pin is used to output

DB8 of the conversion result. When PAR/SER/BYTE SEL = 1, this pin functions

section for more details).

31 to 27

DO

DB[13:9]

Parallel Output Data Bits, DB13 to DB9. When PAR/SER/BYTE SEL = 0, these

pins act as three-state parallel digital input/output pins. When CS and RD

are low, these pins are used to output DB13 to DB9 of the conversion result.

When PAR/SER/BYTE SEL = 1, these pins should be tied to AGND.

32

DO/DI

DB14/

HBEN

DB14/

HBEN

DB14/

HBEN

Parallel Output Data Bit 14 (DB14)/High Byte Enable (HBEN). When PAR/

SER/BYTE SEL = 0, this pin acts as a three-state parallel digital output pin.

When CS and RD are low, this pin is used to output DB14 of the conversion

result. When PAR/SER/BYTE SEL = 1 and DB15/BYTE SEL = 1, the AD7606/

AD7606-6/AD7606-4 operate in parallel byte interface mode. In parallel

byte mode, the HBEN pin is used to select whether the most significant byte

(MSB) or the least significant byte (LSB) of the conversion result is output first.

When HBEN = 1, the MSB is output first, followed by the LSB.

When HBEN = 0, the LSB is output first, followed by the MSB.

In serial mode, this pin should be tied to GND.

33

DO/DI

DB15/

BYTE SEL

DB15/

BYTE SEL

DB15/

BYTE SEL

Parallel Output Data Bit 15 (DB15)/Parallel Byte Mode Select (BYTE SEL).

When PAR/SER/BYTE SEL = 0, this pin acts as a three-state parallel digital

output pin. When CS and RD are low, this pin is used to output DB15 of the

conversion result. When PAR/SER/BYTE SEL = 1, the BYTE SEL pin is used to

select between serial interface mode and parallel byte interface mode

(see Table 8). When PAR/SER/BYTE SEL = 1 and DB15/BYTE SEL = 0, the

AD7606 operates in serial interface mode. When PAR/SER/BYTE SEL = 1

and DB15/BYTE SEL = 1, the AD7606 operates in parallel byte interface mode.

34

DI

REF SELECT

Internal/External Reference Selection Input. Logic input. If this pin is set to

logic high, the internal reference is selected and enabled. If this pin is set to

logic low, the internal reference is disabled and an external reference

voltage must be applied to the REFIN/REFOUT pin.

36, 39

P

REGCAP

Decoupling Capacitor Pin for Voltage Output from Internal Regulator.

These output pins should be decoupled separately to AGND using a 1 μF

capacitor. The voltage on these pins is in the range of 2.5 V to 2.7 V.

相关PDF资料 |

PDF描述 |

|---|---|

| STD09W-Y | WIRE & CABLE MARKERS |

| EVAL-AD7327SDZ | BOARD EVAL FOR AD7327SDZ |

| STD01W-Y | WIRE & CABLE MARKERS |

| MPC8323E-RDB | BOARD REFERENCE DESIGN |

| GMC05DRAH-S734 | CONN EDGECARD 10POS .100 R/A SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD7607EDZ | 功能描述:EVAL BOARD FOR AD7607 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7608EDZ | 功能描述:BOARD EVAL FOR AD7608 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7609EDZ | 功能描述:BOARD EVAL FOR AD7609 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7610CB | 制造商:Analog Devices 功能描述:EVAL KIT FOR 16BIT, 250 KSPS, UNIPOLAR/BIPOLAR PROGRAMMABLE - Bulk |

| EVAL-AD7610CBZ | 功能描述:BOARD EVALUATION FOR AD7610 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:PulSAR® 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

发布紧急采购,3分钟左右您将得到回复。