- 您现在的位置:买卖IC网 > PDF目录17039 > EVAL-AD7664CBZ (Analog Devices Inc)BOARD EVALUATION FOR AD7664 PDF资料下载

参数资料

| 型号: | EVAL-AD7664CBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/24页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD7664 |

| 标准包装: | 1 |

| 系列: | PulSAR® |

| ADC 的数量: | 1 |

| 位数: | 16 |

| 采样率(每秒): | 570k |

| 数据接口: | 串行,并联 |

| 输入范围: | ±VREF |

| 在以下条件下的电源(标准): | 115mW @ 500kSPS |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD7664 |

| 已供物品: | 板 |

| 相关产品: | AD7664ACPZ-ND - IC ADC 16BIT UNIPOLAR 48-LFCSP AD7664ASTZRL-ND - IC ADC 16BIT UNIPOLAR 48LQFP AD7664ASTZ-ND - IC ADC 16BIT UNIPOLAR 48-LQFP |

REV. E

AD7664

–17–

Because the AD7664 is used with a fast throughput, the Mas-

ter Read During Conversion Mode is the most often recom-

mended Serial Mode, when it can be used. In this mode, the

serial clock and data toggle at appropriate instants that mini-

mize potential feedthrough between digital activity and the

critical conversion decisions.

In Read-after-Conversion Mode, it should be noted that, unlike

in other modes, the signal BUSY returns LOW after the 16 data

bits are pulsed out and not at the end of the conversion phase,

which results in a longer BUSY width.

SLAVE SERIAL INTERFACE

External Clock

The AD7664 is configured to accept an externally supplied

serial data clock on the SCLK pin when the EXT/

INT pin is

held HIGH. In this mode, several methods can be used to read

the data. The external serial clock is gated by

CS. When CS and

RD are both LOW, the data can be read after each conversion

or during the following conversion. The external clock can be

either a continuous or discontinuous clock. A discontinuous

clock can be either normally HIGH or normally LOW, when

inactive. Figures 18 and 20 show the detailed timing diagrams of

these methods.

While the AD7664 is performing a bit decision, it is important

that voltage transients not occur on digital input/output pins or

degradation of the conversion result could occur. This is par-

ticularly important during the second half of the conversion

phase, because the AD7664 provides error correction circuitry

that can correct for an improper bit decision made during the

first half of the conversion phase. For this reason, it is recom-

mended that when an external clock is being provided, it is a

discontinuous clock that is toggling only when BUSY is LOW

or, more importantly, that it does not transition during the latter

half of BUSY HIGH.

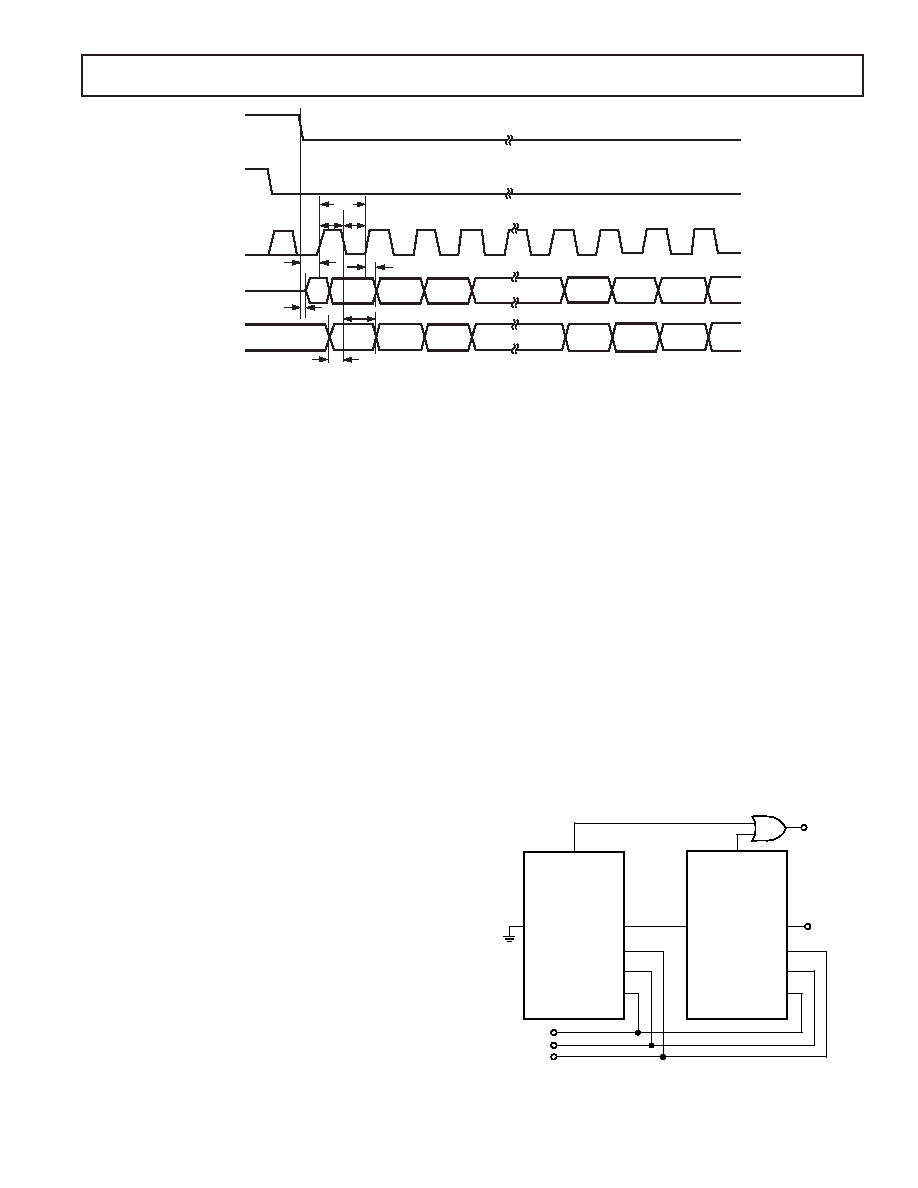

External Discontinuous Clock Data Read after Conversion

Though the maximum throughput cannot be achieved using this

mode, it is the most often recommended of the serial Slave

Modes. Figure 18 shows the detailed timing diagrams of this

method. After a conversion is complete, indicated by BUSY

returning LOW, the result of this conversion can be read

while both

CS and RD are LOW. The data is shifted out,

MSB first, with 16 clock pulses and is valid on both the rising

and falling edge of the clock.

Among the advantages of this method, the conversion perfor-

mance is not degraded, because there are no voltage tran-

sients on the digital interface during the conversion process.

Another advantage is the ability to read the data at any speed up to

40 MHz, which accommodates both slow digital host interface

and the fastest serial reading.

Finally, in this mode only, the AD7664 provides a daisy-chain

feature using the RDC/SDIN input pin for cascading multiple

converters together. This feature is useful for reducing component

count and wiring connections when desired as, for instance, in

isolated multiconverter applications.

An example of the concatenation of two devices is shown in

Figure 19. Simultaneous sampling is possible by using a com-

mon

CNVST signal. It should be noted that the RDC/SDIN

input is latched on the edge of SCLK opposite to the one used

to shift out the data on SDOUT. Therefore, the MSB of the

upstream converter just follows the LSB of the downstream

converter on the next SCLK cycle.

CNVST

CS

SCLK

SDOUT

RDC/SDIN

BUSY

DATA

OUT

AD7664

#1

(DOWNSTREAM)

BUSY

OUT

CNVST

CS

SCLK

AD7664

#2

(UPSTREAM)

RDC/SDIN

SDOUT

SCLK IN

CS IN

CNVST IN

Figure 19. Two AD7664s in a Daisy-Chain Configuration

SCLK

SDOUT

D15

D14

D1

D0

D13

X15

X14

X13

X1

X0

Y15

Y14

CS

BUSY

SDIN

EXT/

INT = 1

INVSCLK = 0

t35

t36 t37

t31

t32

t16

t33

X15

X14

X

12

3

14

15

1617

18

RD = 0

t34

Figure 18. Slave Serial Data Timing for Reading (Read after Convert)

相关PDF资料 |

PDF描述 |

|---|---|

| 0210391035 | CABLE JUMPER 1MM .076M 33POS |

| MPC5510KIT208 | KIT DEVELOPMENT FOR MPC5 |

| MPC5510KIT144 | KIT DEVELOPMENT FOR MPC5 |

| EVAL-AD7661CBZ | BOARD EVALUATION FOR AD7661 |

| DK-START-5AGXB3NES | ARRIA V STARTER KIT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD7665CB | 制造商:AD 制造商全称:Analog Devices 功能描述:Evaluation Board AD766X/AD767X |

| EVAL-AD7665CBZ | 功能描述:BOARD EVALUATION FOR AD7665 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:PulSAR® 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7665EDZ | 功能描述:BOARD EVAL FOR AD76XXEDZ RoHS:否 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7666CBZ | 功能描述:BOARD EVALUATION FOR AD7666 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:PulSAR® 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7667CB | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。