- 您现在的位置:买卖IC网 > PDF目录17048 > EVAL-AD7783EBZ (Analog Devices Inc)BOARD EVAL FOR AD7783 PDF资料下载

参数资料

| 型号: | EVAL-AD7783EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/12页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD7783 |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 24 |

| 采样率(每秒): | 32k |

| 数据接口: | SPI?、QSPI?、MICROWIRE? 和 DSP |

| 输入范围: | ±2.56 V |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD7783 |

| 已供物品: | 板 |

–8–

AD7783

NOISE PERFORMANCE

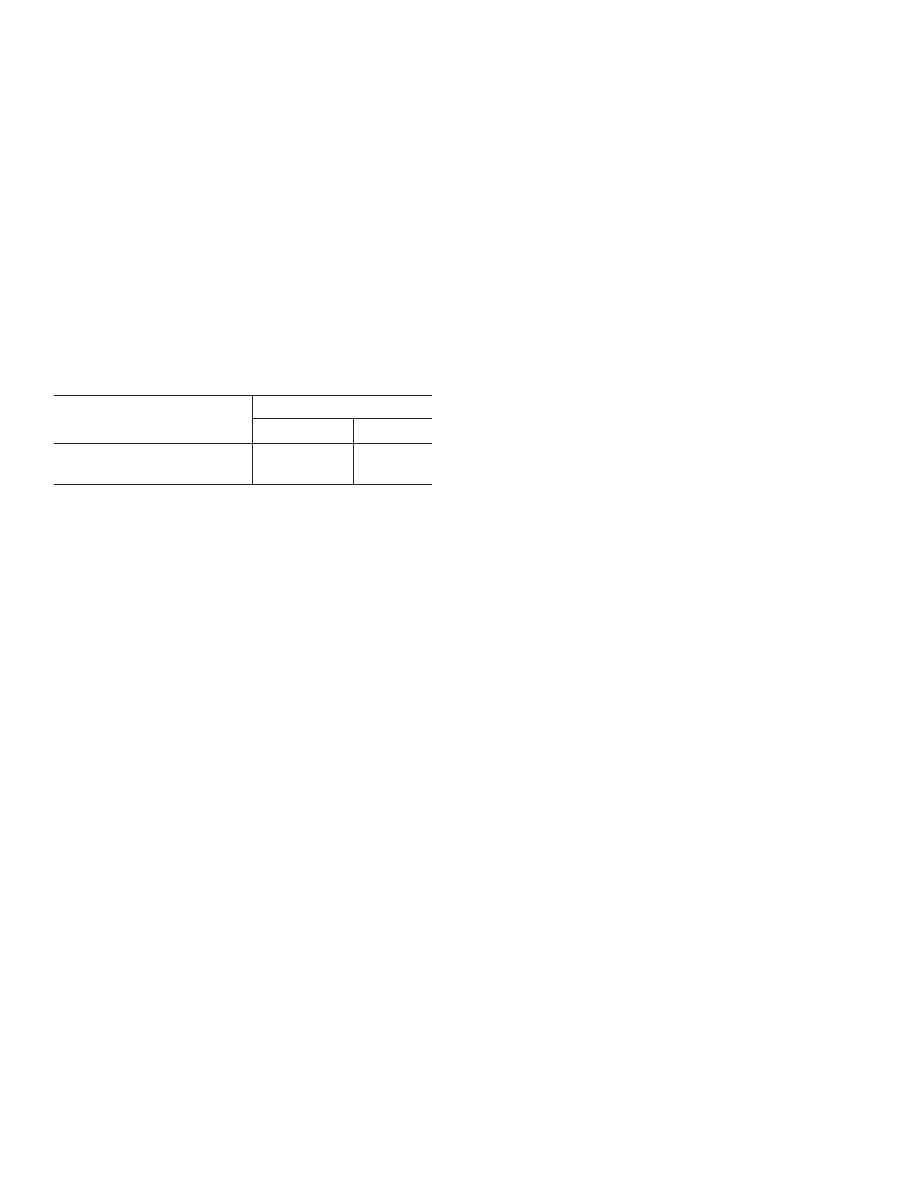

Table I shows the output rms noise and output peak-to-peak

resolution in bits (rounded to the nearest 0.5 LSB) for the two

input voltage ranges. The numbers are typical and are generated

at a differential input voltage of 0 V. The peak-to-peak reso-

lution figures represent the resolution for which there will be

no code flicker within a six-sigma limit. The output noise comes

from two sources. The first is the electrical noise in the semi-

conductor devices (device noise) used in the implementation of

the modulator. Secondly, when the analog input is converted

into the digital domain, quantization noise is added. The device

noise is at a low level and is independent of frequency. The

quantization noise starts at an even lower level but rises rapidly

with increasing frequency to become the dominant noise source.

Table I. Typical Output RMS Noise and

Peak-to-Peak Resolution vs. Input Range

Input Range

±160 mV

±2.56 V

Noise (

mV)

0.65

2.30

Peak-to-Peak Resolution (Bits)

16.5

18.5

DIGITAL INTERFACE

The AD7783’s serial interface consists of four signals:

CS,

SCLK, DOUT/

RDY, and MODE. The MODE pin is used to

select the master/slave mode of operation. When the part is

configured as a master, SCLK is an output; SCLK is an input

when slave mode is selected. Data transfers take place with

respect to this SCLK signal. The DOUT/

RDY line is used

for accessing data from the data register. This pin also functions

as a

RDY line. When a conversion is complete, DOUT/RDY

goes low to indicate that data is ready to be read from the

AD7783’s data register. It is reset high when a read operation

from the data register is complete. It also goes high prior to

the updating of the output register to indicate when not to

read from the device to ensure that a data read is not attempted

while the register is being updated. The digital conversion is

also output on this pin.

CS is used to select the device and to place the device in standby

mode. When

CS is taken low, the AD7783 is powered up, the

PLL locks, and the device initiates a conversion. The device will

continue to convert until

CS is taken high. When CS is taken

high, the AD7783 is placed in standby mode, minimizing the

current consumption. The conversion is aborted, DOUT and

SCLK are three-stated, and the result in the data register is lost.

Figure 2 shows the timing diagram for interfacing to the AD7783

with

CS used to decode the part.

MASTER MODE (MODE = 0)

In this mode, SCLK is provided by the AD7783. With

CS low,

SCLK becomes active when a conversion is complete and gener-

ates 24 falling and rising edges. The DOUT/

RDY pin, which is

normally high, goes low to indicate that a conversion is complete.

Data is output on the DOUT/

RDY pin following the SCLK

falling edge and is valid on the SCLK rising edge. When the

24-bit word has been output, SCLK idles high until the next

conversion is complete. DOUT/

RDY returns high and will remain

high until another conversion is available. It then operates as a

RDY signal again. The part will continue to convert until CS is

taken high. SCLK and DOUT/

RDY are three-stated when CS is

taken high.

SLAVE MODE (MODE = 1)

In slave mode, the SCLK is generated externally. SCLK must

idle high between data transfers. With

CS low, DOUT/RDY

goes low when a conversion is complete. Twenty-four SCLK

pulses are needed to transfer the digital word from the AD7783.

Twenty-four consecutive pulses can be generated or, alterna-

tively, the data transfer can be split into batches. This is useful

when interfacing to a microcontroller that uses 8-bit transfers.

Data is output following the SCLK falling edge and is valid on

the SCLK rising edge.

CIRCUIT DESCRIPTION

Analog Input Channel

The ADC has one fully differential input channel. It feeds into a

high impedance input stage of the buffer amplifier. As a result,

the ADC input can handle significant source impedances and is

tailored for direct connection to external resistive-type sensors,

such as strain gages or resistance temperature detectors (RTDs).

The absolute input voltage range on the ADC input is restricted

to a range between GND + 100 mV and VDD – 100 mV. Care

must be taken in setting up the common-mode voltage and input

voltage range so that these limits are not exceeded; otherwise,

there will be a degradation in linearity and noise performance.

Programmable Gain Amplifier

The output from the buffer on the ADC is applied to the input of

the on-chip programmable gain amplifier (PGA). The PGA gain

range is programmed via the RANGE pin. With an external 2.5 V

reference applied, the PGA can be programmed to have a bipolar

range of

±160 mV (RANGE = 0) or ±2.56 V (RANGE = 1).

These are the ranges that should appear at the input to the

on-chip PGA.

Bipolar Configuration/Output Coding

The analog input on the AD7783 accepts bipolar input voltage

ranges. Signals on the AIN(+) input of the ADC are referenced

REV. C

相关PDF资料 |

PDF描述 |

|---|---|

| GBC25DREI-S13 | CONN EDGECARD 50POS .100 EXTEND |

| EVAL-AD7171EBZ | BOARD EVAL FOR AD7171 |

| HKQ0603S3N8C-T | INDUCTOR HI FREQ 3.8NH 0201 |

| ADR441ARMZ-REEL7 | IC VREF SERIES PREC 2.5V 8-MSOP |

| ECC19DRTN-S13 | CONN EDGECARD 38POS .100 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD7785EBZ | 功能描述:BOARD EVALUATION FOR AD7785 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7787CB | 制造商:Analog Devices 功能描述:DEVELOPMENT BOARD ((NS)) |

| EVAL-AD7787EB | 制造商:Analog Devices 功能描述:LOW PWR, 2CH 24BIT SIGMA-DELTA ADC - Bulk |

| EVAL-AD7788EB | 制造商:Analog Devices 功能描述:Development Tools, Low Power, 16/24Bit Sigma-Delta ADC 制造商:Analog Devices 功能描述:DEV TOOLS, LOW PWR, 16/24BIT SIGMA-DELTA ADC - Bulk |

| EVAL-AD7789EB | 制造商:Analog Devices 功能描述:DEV TOOLS, LOW PWR, 16/24BIT SIGMA-DELTA ADC - Bulk |

发布紧急采购,3分钟左右您将得到回复。