- 您现在的位置:买卖IC网 > PDF目录17057 > EVAL-AD7795EBZ (Analog Devices Inc)BOARD EVAL FOR AD7795 PDF资料下载

参数资料

| 型号: | EVAL-AD7795EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 8/37页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD7795 |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 16 |

| 采样率(每秒): | 470 |

| 数据接口: | SPI?、QSPI?、MICROWIRE? 和 DSP |

| 输入范围: | ±VREF/增益 |

| 在以下条件下的电源(标准): | 2.5mW @ 470SPS |

| 工作温度: | -40°C ~ 105°C |

| 已用 IC / 零件: | AD7795 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

AD7794/AD7795

Rev. D | Page 15 of 36

CHOP DISABLED

With chop disabled, the switching time or settling time is

reduced by a factor of two. However, periodic offset calibrations

may now be required to remove offset and offset drift. When

chop is disabled, the AMP-CM bit in the mode register should

be set to 1. This limits the allowable common-mode voltage that

can be used. However, the common-mode rejection degrades if

the bit is not set.

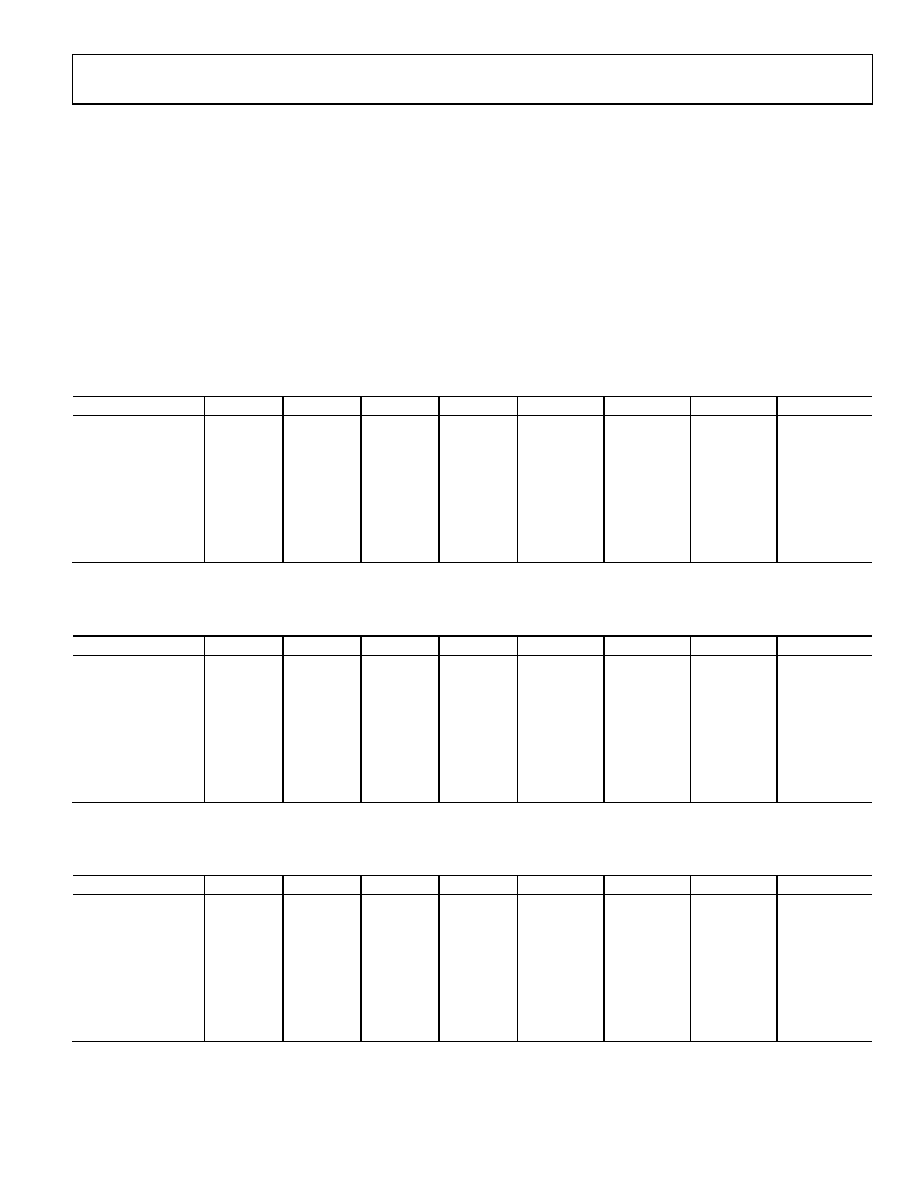

Table 11 shows the rms noise of the AD7794/AD7795 for some

of the update rates and gain settings with chop disabled.

The numbers given are for the bipolar input range with the

internal 1.17 V reference. These numbers are typical and are

generated with a differential input voltage of 0 V.

output peak-to-peak (p-p) resolution is listed in brackets. It is

important to note that the effective resolution is calculated

using the rms noise, while the p-p resolution is calculated based

on peak-to-peak noise. The p-p resolution represents the

resolution for which there is no code flicker. These numbers are

typical and rounded to the nearest LSB.

Table 11. RMS Noise (μV) vs. Gain and Output Update Rate Using an Internal 1.17 V Reference with Chop Disabled

Update Rate (Hz)

Gain of 1

Gain of 2

Gain of 4

Gain of 8

Gain of 16

Gain of 32

Gain of 64

Gain of 128

4.17

1.22

0.98

0.33

0.18

0.13

0.062

0.053

0.051

8.33

1.74

1.53

0.49

0.29

0.21

0.1

0.079

0.07

16.7

2.64

2.44

0.79

0.48

0.33

0.16

0.13

0.12

33.2

4.55

3.52

1.11

0.66

0.46

0.21

0.17

0.16

62

5.03

4.45

1.47

0.81

0.58

0.27

0.2

0.22

123

8.13

7.24

2.27

1.33

0.96

0.48

0.36

0.37

242

15.12

13.18

3.77

2.09

1.45

0.64

0.5

0.47

470

17.18

14.63

8.86

2.96

1.92

0.89

0.69

0.7

Table 12.

Effective Resolution (Bits) vs. Gain and Output Update Rate for the AD7794 Using an Internal 1.17 V Reference with Chop Disabled

Update Rate (Hz)

Gain of 1

Gain of 2

Gain of 4

Gain of 8

Gain of 16

Gain of 32

Gain of 64

Gain of 128

4.17

21 (18.5)

20 (17.5)

21 (18.5)

20.5 (18)

20 (17.5)

19.5 (17)

18.5 (16)

8.33

20.5 (18)

19.5 (17)

20 (17.5)

19.5 (17)

19 (16.5)

18 (15.5)

16.7

20 (17.5)

19 (16.5)

19.5 (17)

19 (16.5)

18 (15.5)

17 (14.5)

33.2

19 (16.5)

18.5 (16)

19 (16.5)

18.5 (16)

17.5 (15)

17 (14.5)

62

19 (16.5)

18 (15.5)

18.5 (16)

18 (15.5)

17.5 (15)

16.5 (14)

123

18 (15.5)

17.5 (15)

18 (15.5)

17.5 (15)

17 (14.5)

16.5 (14)

15.5 (13)

242

17 (14.5)

16.5 (14)

17 (14.5)

16.5 (14)

17 (14.5)

16 (13.5)

15 (12.5)

470

17 (14.5)

16.5 (14)

16 (13.5)

16.5 (14)

16 (13.5)

16.5 (14)

15.5 (13)

14.5 (12)

Table 13.

Effective Resolution (Bits) vs. Gain and Output Update Rate for the AD7795 Using an Internal 1.17 V Reference with Chop Disabled

Update Rate (Hz)

Gain of 1

Gain of 2

Gain of 4

Gain of 8

Gain of 16

Gain of 32

Gain of 64

Gain of 128

4.17

16 (16)

8.33

16 (16)

16 (15.5)

16.7

16 (16)

16 (15.5)

16 (14.5)

33.2

16 (16)

16 (15)

16 (14.5)

62

16 (16)

16 (15.5)

16 (16)

16 (15.5)

16 (15)

16 (14)

123

16 (15.5)

16 (15)

16 (15.5)

16 (15)

16 (14.5)

16 (14)

15.5 (13)

242

16 (14.5)

16 (14)

16 (14.5)

16 (14)

16 (14.5)

16 (13.5)

15 (12.5)

470

16 (14.5)

16 (14)

16 (13.5)

16 (14)

16 (13.5)

16 (14)

15.5 (13)

14.5 (12)

相关PDF资料 |

PDF描述 |

|---|---|

| VI-B1V-EY | CONVERTER MOD DC/DC 5.8V 50W |

| VI-B1W-EY | CONVERTER MOD DC/DC 5.5V 50W |

| MIC2016-1.2YM6 TR | IC DISTRIBUTION SW 1.2A SOT23-6 |

| VE-B1W-EY | CONVERTER MOD DC/DC 5.5V 50W |

| EEM30DRSD | CONN EDGECARD 60POS DIP .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD7796EB | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Power, 16-/24-Bit Sigma-Delta ADC for Bridge Sensors |

| EVAL-AD7796EBZ | 功能描述:BOARD EVALUATION FOR AD7796 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7797EB | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Power, 16-/24-Bit Sigma-Delta ADC for Bridge Sensors |

| EVAL-AD7797EBZ | 功能描述:BOARD EVALUATION FOR AD7797 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7798EB | 制造商:Analog Devices 功能描述:EVAL BD LOW PWR, 16BIT BFFRED SIGMA-DELTA ADC - Bulk |

发布紧急采购,3分钟左右您将得到回复。