- 您现在的位置:买卖IC网 > PDF目录17026 > EVAL-AD977CB (Analog Devices Inc)BOARD EVAL FOR AD977 PDF资料下载

参数资料

| 型号: | EVAL-AD977CB |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/24页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD977 |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 16 |

| 采样率(每秒): | 100k |

| 数据接口: | 串行 |

| 输入范围: | ±10 V |

| 在以下条件下的电源(标准): | 100mW @ 100kSPS |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD977 |

| 已供物品: | 板 |

| 相关产品: | AD977CRSZ-ND - IC ADC 16BIT SRL 100KSPS 28SSOP AD977BRZ-ND - IC ADC 16BIT 100KSPS 20SOIC AD977BRSZ-ND - IC ADC 16BIT 100KSPS 28SSOP AD977BNZ-ND - IC ADC 16BIT 100KSPS 20DIP AD977ARSZ-ND - IC ADC 16BIT 100KSPS 28SSOP AD977ACRZ-ND - IC ADC 16BIT 200KSPS 20SOIC AD977ACRSZ-ND - IC ADC 16BIT 200KSPS 28SSOP AD977ABNZ-ND - IC ADC 16BIT 200KSPS 20DIP AD977ACNZ-ND - IC ADC 16BIT 200KSPS 20DIP AD977AANZ-ND - IC ADC 16BIT 200KSPS 20DIP 更多... |

AD977/AD977A

–13–

REV. D

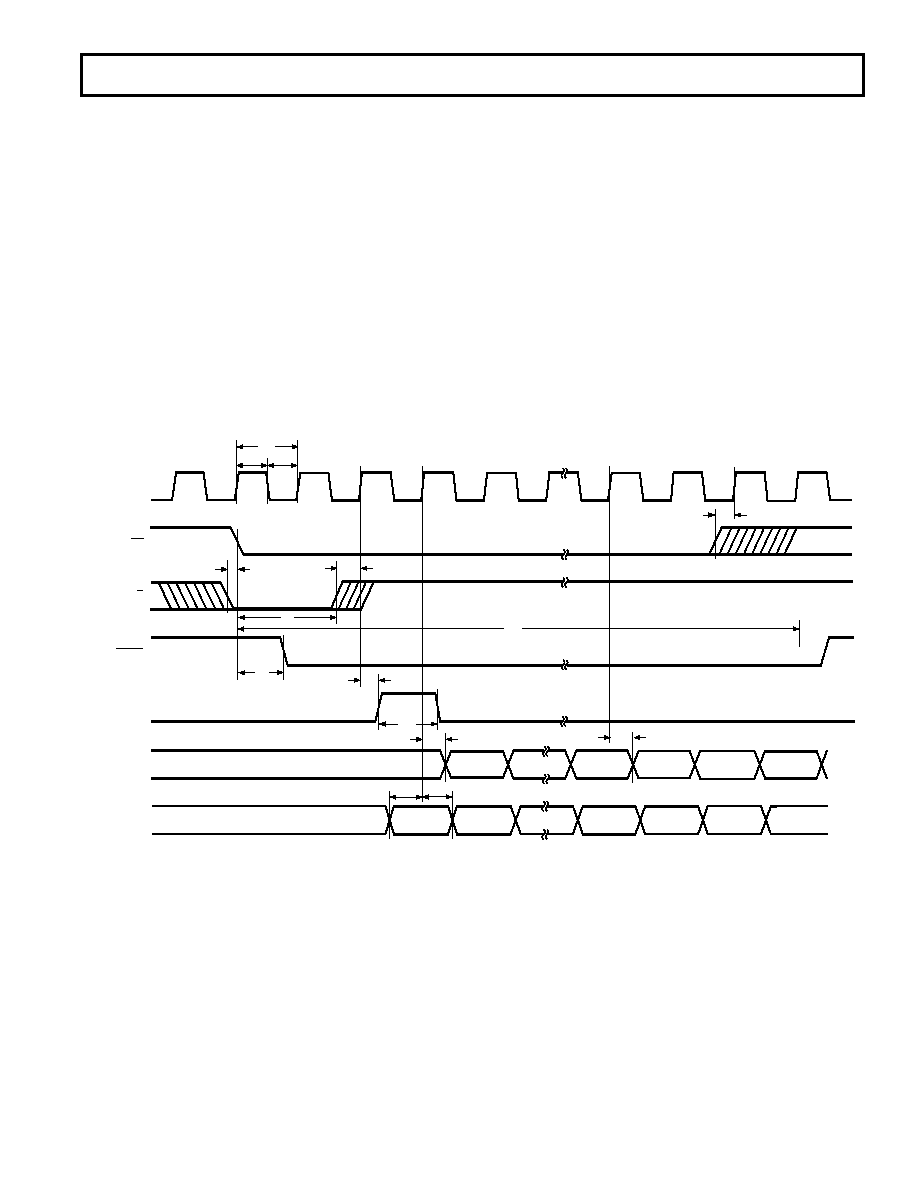

EXTERNAL CONTINUOUS CLOCK DATA READ DURING

CONVERSION WITH SYNC OUTPUT GENERATED

Figure 9 illustrates the method by which data from conversion

“n-1” can be read during conversion “n” while using a continu-

ous external clock with the generation of a SYNC output. What

permits the generation of a SYNC output is a transition of

DATACLK while either

CS is high or while both CS and R/C

are low.

With a continuous clock the

CS pin cannot be tied low as it

could be with a discontinuous clock. Use of a continuous clock

while a conversion is occurring can increase the DNL and

Transition Noise of the AD977/AD977A.

In Figure 9 a conversion is initiated by taking R/

C low with CS

held low. While this condition exists a transition of DATACLK,

clock pulse #0, will enable the generation of a SYNC pulse.

Less then 83 ns after R/

C is taken low the BUSY output will go

low to indicate that the conversion process has began. Figure 9

shows R/

C then going high and after a delay of greater than

15 ns (t15), clock pulse #1 can be taken high to request the

SYNC output. The SYNC output will appear approximately

50 ns after this rising edge and will be valid on the falling edge

of clock pulse #1 and the rising edge of clock pulse #2. The

MSB will be valid approximately 40 ns after the rising edge of

clock pulse #2 and can be latched off either the falling edge of

clock pulse #2 or the rising edge of clock pulse #3. The LSB

will be valid on the falling edge of clock pulse #17 and the rising

edge of clock pulse #18. Approximately 40 ns after the rising

edge of clock pulse #18, the DATA output pin will reflect the

state of the TAG input pin during the rising edge of clock

pulse #2.

For both the AD977 and the AD977A the data should be

clocked out during the 1st half of

BUSY so as not to degrade

conversion performance. For the AD977 this requires use of a

4.8 MHz DATACLK or greater with data being read out as

soon as the conversion process begins. For the AD977A it

requires use of a 10 MHz DATACLK or greater.

CS

BUSY

R/C

EXT

DATACLK

BIT 15

(MSB)

1

DATA

SYNC

03

BIT 0

(LSB)

TAG 0

TAG 1

TAG 0

TAG

2

t13

t14

t12

t19

18

t15

t16

t1

t20

t2

t17

t12

t18

t23

t24

t18

TAG 2

TAG 1

TAG 16

TAG 17

TAG 18

TAG 19

Figure 9. Conversion and Read Timing for Reading Previous Conversion Results During a Conversion Using An External

Continuous Data Clock (EXT/

INT Set to Logic High)

相关PDF资料 |

PDF描述 |

|---|---|

| CDB5529 | EVAL BOARD FOR CS5529 |

| VE-J1F-EY | CONVERTER MOD DC/DC 72V 50W |

| GCM22DSXH | CONN EDGECARD 44POS DIP .156 SLD |

| CDB5368 | BOARD EVAL FOR CS5368 192KHZ ADC |

| VE-J1B-EY | CONVERTER MOD DC/DC 95V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD9830EBZ | 功能描述:BOARD EVALUATION AD9830 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-AD9831EB | 制造商:Analog Devices 功能描述: |

| EVAL-AD9831EBZ | 功能描述:BOARD EVALUATION AD9831 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-AD9832EB | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk 制造商:Analog Devices 功能描述:AD9832 EVAL BOARD |

| EVAL-AD9832SDZ | 功能描述:BOARD EVAL FOR AD9832 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

发布紧急采购,3分钟左右您将得到回复。