- 您现在的位置:买卖IC网 > PDF目录16594 > EVAL-AD9835SDZ (Analog Devices Inc)BOARD EVAL FOR AD9835 PDF资料下载

参数资料

| 型号: | EVAL-AD9835SDZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/28页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9835 |

| 标准包装: | 1 |

| 主要目的: | 计时,直接数字合成(DDS) |

| 已用 IC / 零件: | AD9835 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

Data Sheet

AD9835

Rev. A | Page 17 of 28

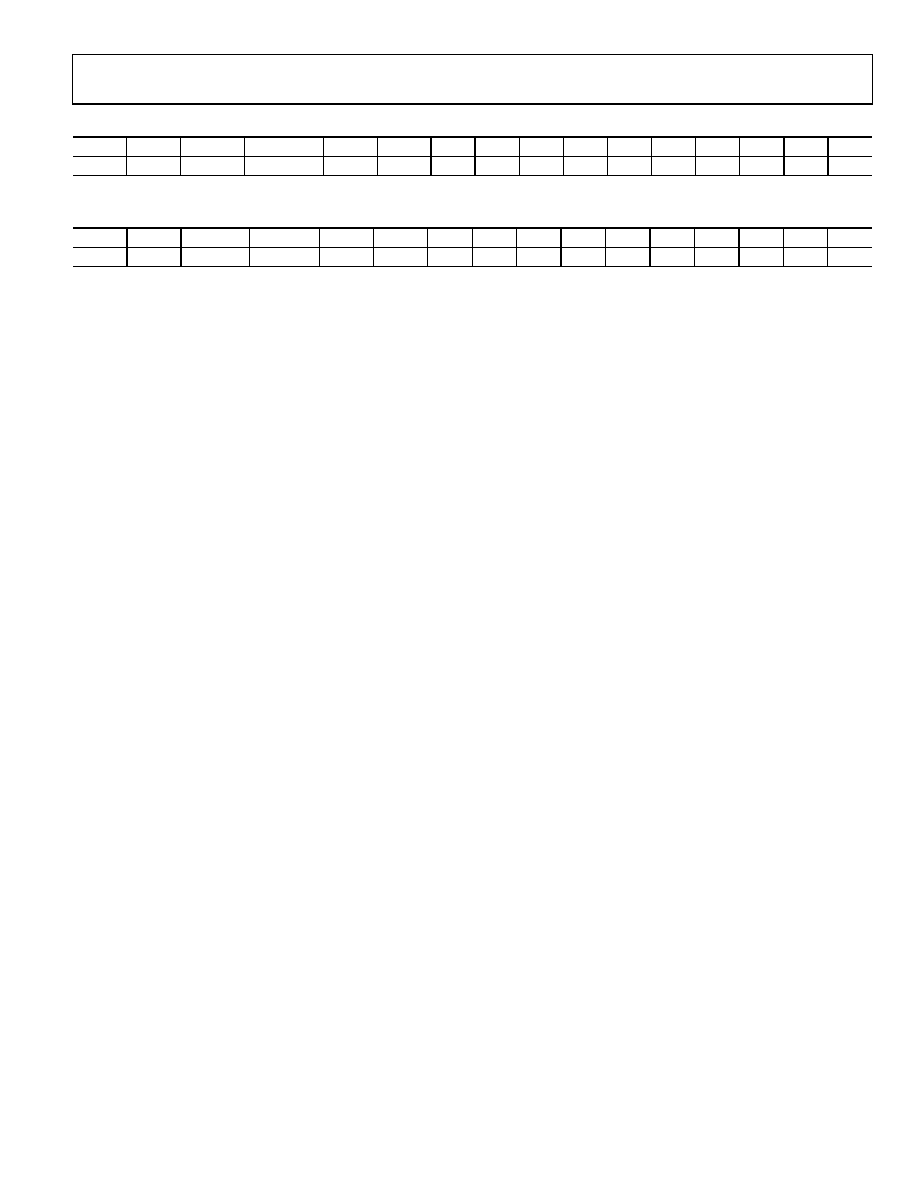

Table 12. Setting SYNC and SELSRC

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

1

0

SYNC

SELSRC

X1

X1

X1

X1

1 X = don’t care.

Table 13. Power-Down, Resetting and Clearing the AD9835

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

1

SLEEP

RESET

CLR

X1

X1

1 X = don’t care.

Transfer of the data from the 16-bit data register to the

destination register or from the FSELECT/PSEL register to the

respective multiplexer occurs on the next MCLK rising edge.

Because SCLK and MCLK are asynchronous, an MCLK rising

edge may occur while the data bits are in a transitional state.

This can cause a brief spurious DAC output if the register being

written to is generating the DAC output. To avoid such spurious

outputs, the AD9835 contains synchronizing circuitry.

When the SYNC bit is set to 1, the synchronizer is enabled and

data transfers from the serial register (defer register) to the 16-bit

data register, and the FSELECT/PSEL registers occur following

a two-stage pipeline delay that is triggered on the MCLK falling

edge. The pipeline delay ensures that the data is valid when the

transfer occurs. Similarly, selection of the frequency/phase

registers using the FSELECT/PSELx pins is synchronized with

the MCLK rising edge when SYNC = 1. When SYNC = 0, the

synchronizer is bypassed.

Selecting the frequency/phase registers using the pins is

synchronized with MCLK internally also when SYNC = 1 to

ensure that these inputs are valid at the MCLK rising edge. If

times t11 and t11A are met, then the inputs will be at steady state

at the MCLK rising edge. However, if times t11 and t11A are

violated, the internal synchronizing circuitry will delay the

instant at which the pins are sampled, ensuring that the inputs

are valid at the sampling instant (see Figure 5).

LATENCY

Associated with each operation is a latency. When inputs

FSELECT/PSEL change value, there is a pipeline delay before

control is transferred to the selected register; there is a pipeline

delay before the analog output is controlled by the selected

register. When times t11 and t11A are met, PSEL0, PSEL1, and

FSELECT have latencies of six MCLK cycles when SYNC = 0.

When SYNC = 1, the latency is increased to 8 MCLK cycles.

When times t11 and t11A are not met, the latency can increase by

one MCLK cycle. Similarly, there is a latency associated with

each write operation. If a selected frequency/phase register is

loaded with a new word, there is a delay of 6 to 7 MCLK cycles

before the analog output will change (there is an uncertainty of

one MCLK cycle regarding the MCLK rising edge at which the

data is loaded into the destination register). When SYNC = 1,

the latency is 8 or 9 MCLK cycles.

FLOWCHARTS

The flowchart in Figure 22 shows the operating routine for the

reset, which resets the phase accumulator to zero so that the

analog output is at midscale. To avoid spurious DAC outputs

while the AD9835 is being initialized, the RESET bit should be

set to 1 until the part is ready to begin generating an output.

Taking CLR high sets SYNC and SELSRC to 0 so that the

FSELECT/PSELx pins are used to select the frequency/phase

registers, and the synchronization circuitry is bypassed. A write

operation is needed to the SYNC/SELSRC register to enable the

synchronization circuitry or to change control to the FSELECT/

PSEL bits.

RESET does not reset the phase and frequency registers. These

registers will contain invalid data and, therefore, should be set to

a known value by the user. The RESET bit is then set to 0 to begin

generating an output. A signal will appear at the DAC output 6

MCLK cycles after RESET is set to 0.

The analog output is fMCLK/232 × FREG, where FREG is the value

loaded into the selected frequency register. This signal is phase

shifted by the amount specified in the selected phase register

(2π/4096 × PHASEx REG, where PHASEx REG is the value

contained in the selected phase register).

Control of the frequency/phase registers can be interchanged

from the pins to the bits.

相关PDF资料 |

PDF描述 |

|---|---|

| MCZ33689DEW | IC SYSTEM BASIS CHIP LIN 32-SOIC |

| EVAL-AD5165EBZ | BOARD EVALUATION FOR AD5165 |

| ESM08DRTI | CONN EDGECARD 16POS DIP .156 SLD |

| EVAL-ADCMP601BKSZ | BOARD EVAL FOR ADCMP601 SC70-5 |

| RMC05DRYS-S93 | CONN EDGECARD 10POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD9837SDZ | 功能描述:BOARD EVAL FOR AD9837 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-AD9838SDZ | 功能描述:BOARD EVAL FOR AD9838 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-AD9880-ABZ | 功能描述:KIT MODULE VIDEO INPUT AD9880 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| EVAL-ADAS1000EBZU1 | 功能描述:EVAL BOARD ADAS1000 ECG AFE RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板 |

| EVAL-ADAS1000SDZ | 功能描述:数据转换 IC 开发工具 EVALUATION BOARD RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

发布紧急采购,3分钟左右您将得到回复。