- 您现在的位置:买卖IC网 > PDF目录16522 > EVAL-ADAU1781Z (Analog Devices Inc)BOARD EVAL FOR ADAU1781 PDF资料下载

参数资料

| 型号: | EVAL-ADAU1781Z |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/92页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR ADAU1781 |

| 标准包装: | 1 |

| 系列: | SigmaDSP® |

| 主要目的: | 音频编解码器 |

| 嵌入式: | 是,DSP |

| 已用 IC / 零件: | ADAU1781 |

| 主要属性: | 立体声,24 位,8 ~ 96 kHz 采样率,GUI 工具 |

| 次要属性: | * |

| 已供物品: | * |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

ADAU1781

Rev. B| Page 11 of 92

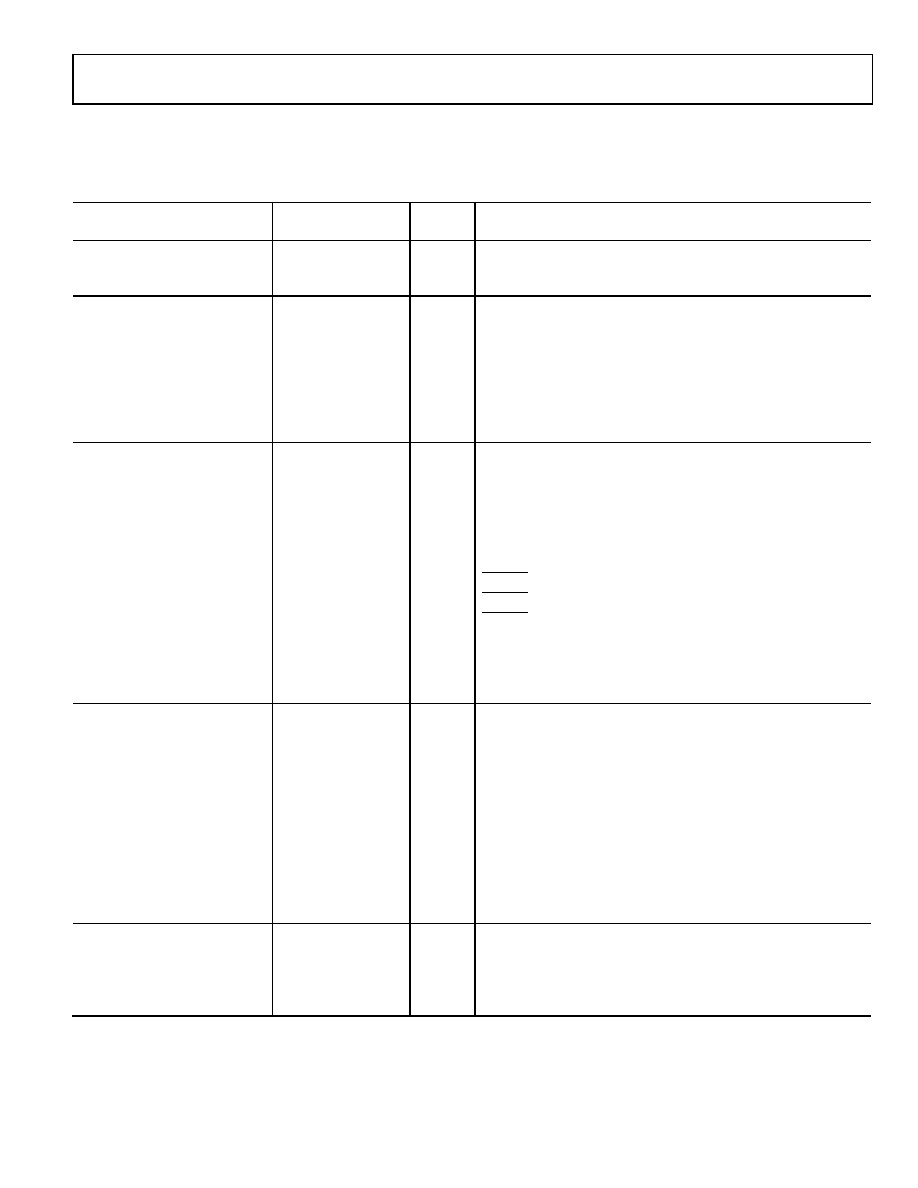

DIGITAL TIMING SPECIFICATIONS

25°C < TA < +85°C, IOVDD = 1.62 V to 3.63 V, unless otherwise specified.

Table 7. Digital Timing

Limit

Parameter

t

MIN

t

MAX

Unit

Description

MASTER CLOCK

t

MP

50

90.9

ns

Master clock (MCLK) period (that is, period of the signal input to MCKI).

Duty Cycle

30

70

%

SERIAL PORT

t

BIL

10

ns

BCLK pulse width low.

t

BIH

10

ns

BCLK pulse width high.

t

LIS

5

ns

LRCLK setup. Time to BCLK rising.

t

LIH

5

ns

LRCLK hold. Time from BCLK rising.

t

SIS

5

ns

DAC_SDATA setup. Time to BCLK rising.

t

SIH

5

ns

DAC_SDATA hold. Time from BCLK rising.

t

SODM

70

ns

ADC_SDATA delay. Time from BCLK falling in master mode.

SPI PORT

f

CCLK,R

5

MHz

CCLK frequency, read operation, IOVDD = 1.8 V ± 10%.

f

CCLK,R

10

MHz

CCLK frequency, read operation, IOVDD = 3.3 V ± 10%.

f

CCLK,W

25

MHz

CCLK frequency, write operation, IOVDD = 1.8 V ± 10%.

f

CCLK,W

25

MHz

CCLK frequency, write operation, IOVDD = 3.3 V ± 10%.

t

CCPL

10

ns

CCLK pulse width low.

t

CCPH

10

ns

CCLK pulse width high.

t

CLS

10

ns

CLATCH setup. Time to CCLK rising.

t

CLH

5

ns

CLATCH hold. Time from CCLK rising.

t

CLPH

10

ns

CLATCH pulse width high.

t

CDS

5

ns

CDATA setup. Time to CCLK rising.

t

CDH

5

ns

CDATA hold. Time from CCLK rising.

t

COD

70

COUT delay from CCLK edge to valid data, IOVDD = 1.8 V ± 10%.

40

ns

COUT delay from CCLK edge to valid data, IOVDD = 3.3 V ± 10%.

I2C PORT

f

SCL

400

kHz

SCL frequency.

t

SCLH

0.6

s

SCL high.

t

SCLL

1.3

s

SCL low.

t

SCS

0.6

s

Setup time; relevant for repeated start condition.

t

SCH

0.6

s

Hold time. After this period, the first clock is generated.

t

DS

100

ns

Data setup time.

t

SCR

300

ns

SCL rise time.

t

SCF

300

ns

SCL fall time.

t

SDR

300

ns

SDA rise time.

t

SDF

300

ns

SDA fall time.

t

BFT

0.6

s

Bus-free time. Time between stop and start.

DIGITAL MICROPHONE

R

L = 1 M, CL = 14 pF.

t

DCF

10

ns

Digital microphone clock fall time.

t

DCR

10

ns

Digital microphone clock rise time.

t

DDV

22

30

ns

Digital microphone delay time for valid data.

t

DDH

0

12

ns

Digital microphone delay time for data three-stated.

相关PDF资料 |

PDF描述 |

|---|---|

| MCP1316T-46BE/OT | IC SPRVSR SMPL RSET 4.6V SOT23-5 |

| EBM28DTBN-S189 | CONN EDGECARD 56POS R/A .156 SLD |

| 6374110-4 | C/A SM, LC TO LC 4METER |

| EBM28DTBH-S189 | CONN EDGECARD 56POS R/A .156 SLD |

| VI-J0F-EZ-S | CONVERTER MOD DC/DC 72V 25W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADAU1962AZ | 制造商:Analog Devices 功能描述:EVAL BOARD FOR ADAU1962A - Boxed Product (Development Kits) 制造商:Analog Devices 功能描述:Eval Board for ADAU1962A |

| EVAL-ADAU1966AZ | 制造商:Analog Devices 功能描述:EVAL BOARD FOR ADAU1962A - Boxed Product (Development Kits) |

| EVAL-ADAU1966Z | 功能描述:BOARD EVAL FOR ADAU1966 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-ADAU1966Z | 制造商:Analog Devices 功能描述:ADAU1966, DAC, SIGMA DELTA, SPI, I2C, EV |

| EVAL-ADAU1978Z | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad Analog-to-Digital Converter (ADC) |

发布紧急采购,3分钟左右您将得到回复。