- 您现在的位置:买卖IC网 > PDF目录16855 > EVAL-ADF4350EB2Z (Analog Devices Inc)EVALUATION BOARD 2 FOR ADF4350 PDF资料下载

参数资料

| 型号: | EVAL-ADF4350EB2Z |

| 厂商: | Analog Devices Inc |

| 文件页数: | 17/32页 |

| 文件大小: | 0K |

| 描述: | EVALUATION BOARD 2 FOR ADF4350 |

| 标准包装: | 1 |

| 主要目的: | 计时,频率合成器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | ADF4350 |

| 主要属性: | 带 VCO 的单路分数-N 和整数-N PLL |

| 次要属性: | USB 接口 |

| 已供物品: | 板,缆线,CD |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

ADF4350

Rev. A | Page 24 of 32

SPUR CONSISTENCY AND FRACTIONAL SPUR

OPTIMIZATION

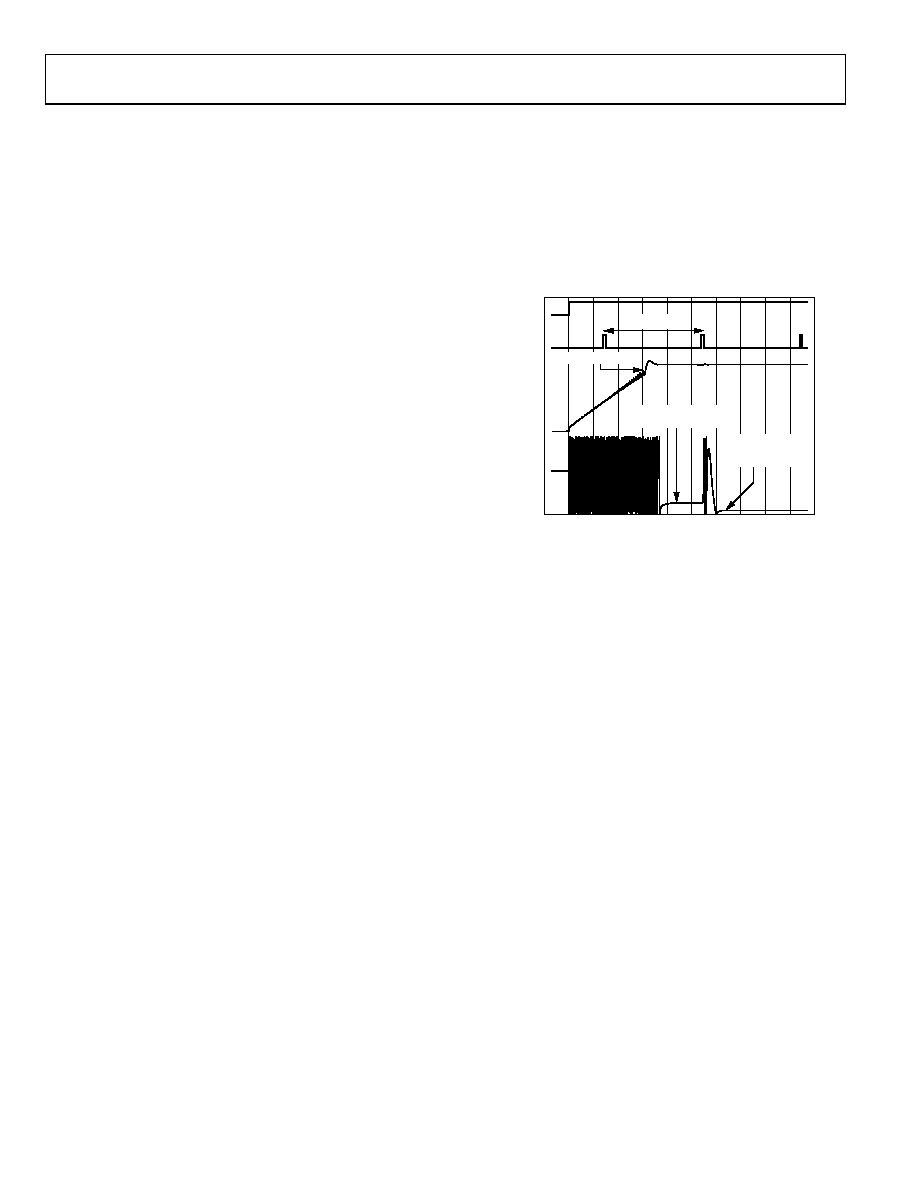

When a new frequency is programmed, the second sync pulse

after the LE rising edge is used to resynchronize the output

phase to the reference. The tSYNC time is to be programmed to

a value that is as least as long as the worst-case lock time. This

guarantees the phase resync occurs after the last cycle slip in the

PLL settling transient.

With dither off, the fractional spur pattern due to the quantiza-

tion noise of the SDM also depends on the particular phase

word with which the modulator is seeded.

The phase word can be varied to optimize the fractional and

subfractional spur levels on any particular frequency. Thus, a

look-up table of phase values corresponding to each frequency

can be constructed for use when programming the ADF4350.

In the example shown in Figure 33, the PFD reference is 25 MHz

and MOD = 125 for a 200 kHz channel spacing. tSYNC is set to

400 μs by programming CLK_DIV_VALUE = 80.

LE

PHASE

FREQUENCY

SYNC

(INTERNAL)

–100

0

100

200

1000

300

400

500

600 700 800

900

0

73

25-

020

TIME (s)

PLL SETTLES TO

CORRECT PHASE

AFTER RESYNC

tSYNC

LAST CYCLE SLIP

PLL SETTLES TO

INCORRECT PHASE

If a look-up table is not used, keep the phase word at a constant

value to ensure consistent spur levels on any particular frequency.

PHASE RESYNC

The output of a fractional-N PLL can settle to any one of the

MOD phase offsets with respect to the input reference, where

MOD is the fractional modulus. The phase resync feature in the

ADF4350 produces a consistent output phase offset with respect

to the input reference. This is necessary in applications where the

output phase and frequency are important, such as digital beam

forming. See the Phase Programmability section to program a

specific RF output phase when using phase resync.

Phase resync is enabled by setting Bits [DB16:DB15] in

Register 3 to 1, 0. When phase resync is enabled, an internal

timer generates sync signals at intervals of tSYNC given by the

following formula:

Figure 33. Phase Resync Example

Phase Programmability

The phase word in Register 1 controls the RF output phase. As

this word is swept from 0 to MOD, the RF output phase sweeps

over a 360° range in steps of 360°/MOD.

tSYNC = CLK_DIV_VALUE × MOD × tPFD

where:

tPFD is the PFD reference period.

CLK_DIV_VALUE is the decimal value programmed in

Bits [DB14:DB3] of Register 3 and can be any integer in the

range of 1 to 4095.

MOD is the modulus value programmed in Bits [DB14:DB3] of

Register 1 (R1).

相关PDF资料 |

PDF描述 |

|---|---|

| RNF-100-3/4-BK-STK | HEATSHRINK RNF-100 3/4"X4' BLK |

| A1BXH-1436G | IDC CABLE - ASR14H/AE14G/X |

| EVAL-ADF4350EB1Z | EVALUATION BOARD 1 FOR ADF4350 |

| RNF-100-3/8-BK-STK | HEATSHRINK RNF-100 3/8"X4' BLK |

| 8726034006 | HEAT SHRINK TUBING |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADF4351EB1Z | 功能描述:BOARD 1 EVAL FOR ADF4351 RoHS:否 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-ADF4360-0EB1 | 制造商:AD 制造商全称:Analog Devices 功能描述:Integrated Synthesizer and VCO |

| EVAL-ADF4360-1EB1 | 制造商:Analog Devices 功能描述:Evaluation Board For ADF4360-1 |

| EVAL-ADF4360-1EBZ1 | 功能描述:BOARD EVALUATION FOR ADF4360-1 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板 |

| EVAL-ADF4360-2EB1 | 制造商:Analog Devices 功能描述:EVALUATION BOARD FOR ADF4360-2 |

发布紧急采购,3分钟左右您将得到回复。